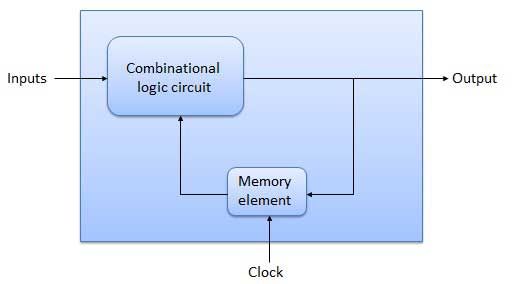

Los diferentes tipos de sistemas digitales se construyen a partir de muy pocos tipos de configuraciones de red básicas, como la puerta Y, la puerta NAND, la puerta O, etc. Estos circuitos elementales se utilizan una y otra vez en varias combinaciones topológicas. Además de realizar lógica, los sistemas digitales también deben almacenar números binarios. Para estas células de memoria, también conocidas como CHANCLAS' s están diseñados. Para realizar algunas funciones como la suma binaria. Por tanto, para realizar tales funciones, combinaciones de puertas lógicas y los FLIP-FLOP están diseñados sobre un circuito integrado de un solo chip. Estos IC forman los bloques de construcción prácticos de los sistemas digitales. Uno de esos bloques de construcción que se utilizan para la suma binaria es el sumador de avance anticipado.

¿Qué es un sumador anticipado de acarreo?

Una computadora digital debe contener circuitos que puedan realizar operaciones aritméticas como suma, resta, multiplicación y división. Entre estos, la suma y la resta son las operaciones básicas, mientras que la multiplicación y la división son la suma y la resta repetidas, respectivamente.

Para realizar estas operaciones, se implementan 'circuitos sumadores' utilizando puertas lógicas básicas. Circuitos sumadores evolucionan como Half-sumador, Sumador completo, Sumador de acarreo de ondulación y Sumador de avance anticipado.

Entre estos Carry Look-ahead Adder es el circuito sumador más rápido. Reduce el retardo de propagación, que se produce durante la adición, mediante el uso de circuitos de hardware más complejos. Está diseñado transformando el circuito sumador de acarreo de ondulación de modo que la lógica de acarreo del sumador se cambie a lógica de dos niveles.

Sumador de avance de transporte de 4 bits

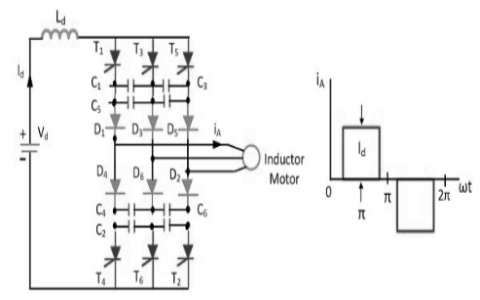

En los sumadores paralelos, la salida de acarreo de cada sumador completo se da como entrada de acarreo al siguiente estado de orden superior. Por lo tanto, con estos sumadores no es posible producir salidas de acarreo y suma de ningún estado a menos que esté disponible una entrada de acarreo para ese estado.

Entonces, para que ocurra el cálculo, el circuito tiene que esperar hasta que el bit de acarreo se propague a todos los estados. Esto induce un retardo de propagación de acarreo en el circuito.

Sumador de portador de ondulación de 4 bits

Considere el circuito sumador de acarreo de ondulación de 4 bits anterior. Aquí, la suma S3 se puede producir tan pronto como se den las entradas A3 y B3. Pero el acarreo C3 no se puede calcular hasta que se aplique el bit de acarreo C2, mientras que C2 depende de C1. Por lo tanto, para producir resultados finales de estado estable, el acarreo debe propagarse a través de todos los estados. Esto aumenta el retardo de propagación de acarreo del circuito.

El retardo de propagación del sumador se calcula como 'el retardo de propagación de cada puerta multiplicado por el número de etapas del circuito'. Para el cálculo de una gran cantidad de bits, se deben agregar más etapas, lo que empeora mucho el retraso. Por lo tanto, para resolver esta situación, se introdujo Carry Look-ahead Adder.

Para comprender el funcionamiento de un sumador de avance anticipado, a continuación se describe un sumador de avance anticipado de 4 bits.

Diagrama de lógica de sumador de avance de avance de 4 bits

En este sumador, la entrada de acarreo en cualquier etapa del sumador es independiente de los bits de acarreo generados en las etapas independientes. Aquí la salida de cualquier etapa depende solo de los bits que se agregan en las etapas anteriores y de la entrada de acarreo proporcionada en la etapa inicial. Por lo tanto, el circuito en cualquier etapa no tiene que esperar la generación del bit de acarreo de la etapa anterior y el bit de acarreo se puede evaluar en cualquier momento.

Tabla de verdad del sumador anticipado de acarreo

Para derivar la tabla de verdad de este sumador, se introducen dos términos nuevos: llevar generar y llevar propagar. Carry generate Gi = 1 siempre que se genere un carry Ci + 1. Depende de las entradas Ai y Bi. Gi es 1 cuando tanto Ai como Bi son 1. Por tanto, Gi se calcula como Gi = Ai. Bi.

El acarreo de Pi propagado está asociado con la propagación del acarreo de Ci a Ci + 1. Se calcula como Pi = Ai ⊕ Bi. La tabla de verdad de este sumador puede derivarse de la modificación de la tabla de verdad de un sumador completo.

Usando los términos Gi y Pi, la suma Si y Carry Ci + 1 se dan a continuación:

- Si = Pi ⊕ Gi.

- Ci + 1 = Ci.Pi + Gi.

Por lo tanto, los bits de acarreo C1, C2, C3 y C4 se pueden calcular como

- C1 = C0.P0 + G0.

- C2 = C1.P1 + G1 = (C0.P0 + G0) .P1 + G1.

- C3 = C2.P2 + G2 = (C1.P1 + G1) .P2 + G2.

- C4 = C3.P3 + G3 = C0.P0.P1.P2.P3 + P3.P2.P1.G0 + P3.P2.G1 + G2.P3 + G3.

Se puede observar en las ecuaciones que transportan Ci + 1 solo depende del acarreo C0, no de los bits de acarreo intermedios.

Carry-Look-ahead-Adder-Truth-Table

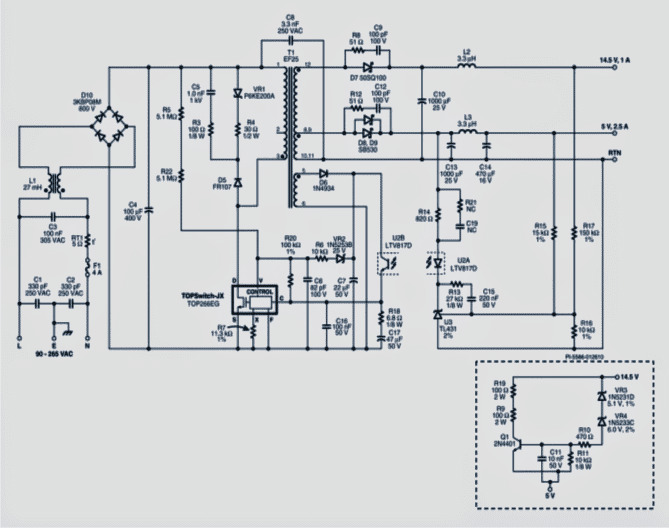

Diagrama de circuito

Las ecuaciones anteriores se implementan utilizando circuitos combinacionales de dos niveles junto con puertas Y, O, donde se supone que las puertas tienen múltiples entradas.

Carry-Output-Generation-Circuit-of-Carry-Look-ahead-Adder

A continuación, se muestra el circuito sumador de avance anticipado de 4 bits.

Diagrama de circuito de sumador de anticipación de acarreo de 4 bits

Los circuitos sumadores de avance anticipado de 8 y 16 bits se pueden diseñar conectando en cascada el circuito sumador de 4 bits con lógica de acarreo.

Ventajas de Carry Look-ahead Adder

En este sumador, se reduce el retardo de propagación. La salida de acarreo en cualquier etapa depende solo del bit de acarreo inicial de la etapa inicial. Con este sumador es posible calcular los resultados intermedios. Este sumador es el sumador más rápido utilizado para el cálculo.

Aplicaciones

Los sumadores anticipados de acarreo de alta velocidad se utilizan como implementados como IC. Por tanto, es fácil incrustar el sumador en circuitos. Combinando dos o más sumadores, los cálculos de funciones booleanas de bits superiores se pueden realizar fácilmente. Aquí, el aumento en el número de puertas también es moderado cuando se usa para bits más altos.

Para este sumador hay una compensación entre el área y la velocidad. Cuando se utiliza para cálculos de bits más altos, proporciona alta velocidad, pero la complejidad del circuito también aumenta, aumentando así el área ocupada por el circuito. Este sumador generalmente se implementa como módulos de 4 bits que se conectan en cascada cuando se usan para cálculos más altos. Este sumador es más costoso en comparación con otros sumadores.

Para el cálculo booleano en computadoras, los sumadores se utilizan con regularidad. Charles Babbage implementó un mecanismo para anticipar el bit de acarreo en las computadoras, para reducir el retraso causado por el sumadores de transporte de ondulación . Al diseñar un sistema, la velocidad de cálculo es el factor decisivo más importante para un diseñador. En 1957, Gerald B. Rosenberger patentó el sumador Binary Carry Look-ahead. Sobre la base del análisis del retardo de la puerta y la simulación, se están realizando experimentos para modificar el circuito de este sumador para hacerlo aún más rápido. Para un sumador de anticipación de acarreo de n bits, ¿cuál es el retardo de propagación, cuando se da un retardo de cada puerta de 20?

Credito de imagen