El proceso de diseño de hardware digital se ha transformado intensamente en los últimos años. Por lo tanto, se pueden implementar pequeños circuitos digitales utilizando PAL y PLA. Cada dispositivo se utiliza para implementar varios circuitos que no necesitan más que la cantidad de i / ps, o / ps y términos de producto que se ofrecen en el chip específico. Estos chips son inadecuados para tamaños bastante modestos, y normalmente admiten un número mutuo de entradas y salidas de no más de 32. Para el diseño de estos circuitos que necesitan más entradas y salidas, se pueden emplear numerosos PLA / PAL o un tipo más elegante de chip se puede utilizar llamado CPLD (dispositivo lógico programable complejo). Un chip CPLD incluye varios bloques de circuitos en un solo chip con recursos de cableado internos para conectar los bloques de circuitos. Cada bloque de circuito es comparable a un PLA o PAL.

¿Qué es un dispositivo lógico programable complejo?

El acrónimo de CPLD es 'Dispositivos lógicos programables complejos', es un tipo de circuito integrado que los diseñadores de aplicaciones diseñan para implementar hardware digital como teléfonos móviles. Estos pueden manejar diseños a sabiendas más altos que los SPLD (dispositivos lógicos programables simples), pero ofrecen menos lógica que los FPGA ( matriz de puertas programables Los CPLD incluyen numerosos bloques lógicos, cada uno de los bloques incluye 8-16 macrocélulas. Debido a que cada bloque lógico ejecuta una función específica, todas las macrocélulas en un bloque lógico están completamente conectadas. Dependiendo del uso, estos bloques pueden o no estar conectados entre sí.

Dispositivo lógico programable complejo

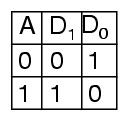

La mayoría de los CPLD (dispositivos lógicos programables complejos) tienen macrocélulas con una suma de función lógica y una función electiva FF (flip-flop) . Dependiendo del chip, la función lógica combinatoria admite de 4 a 16 términos de producto con fan-in inclusivo. Los CPLD también difieren en términos de registros de desplazamiento y puertas lógicas. Por esta razón, se pueden utilizar CPLD con una gran cantidad de puertas lógicas en lugar de FPGA. Otra especificación de CPLD significa el número de términos de producto que puede lograr una macrocélula. Los términos de producto son el producto de señales digitales que ejecutan una función lógica específica.

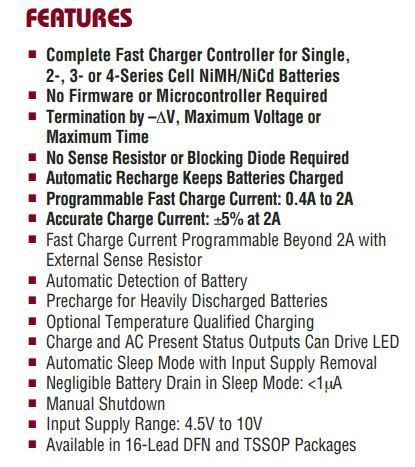

Los CPLD están disponibles en varios formatos de paquetes IC y familias lógicas. Los CPLD también difieren en términos de voltaje de suministro, corriente de operación, corriente de reserva y disipación de energía. Además, estos se pueden obtener con varias cantidades de memoria y varios tipos de soporte de memoria. Generalmente, la memoria se expresa en bits / megabits. El soporte de memoria consiste en ROM, RAM y RAM de doble puerto. También consta de CAM (memoria direccionable de contenido), así como memoria FIFO (primero en entrar, primero en salir) y LIFO (último en entrar, último en salir).

Arquitectura de dispositivo lógico programable complejo

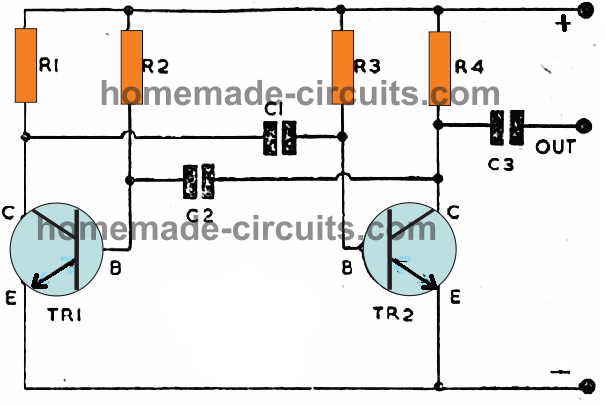

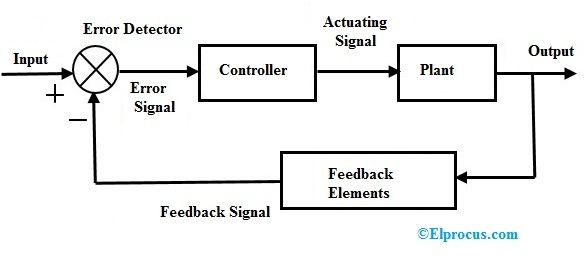

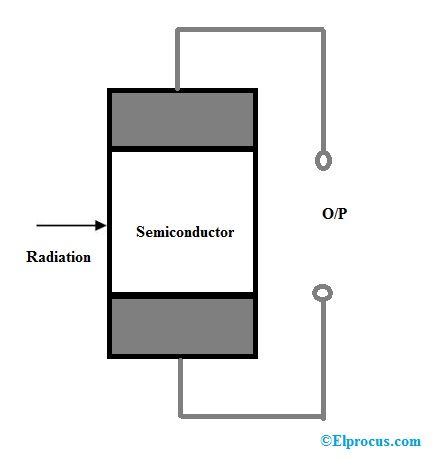

Un dispositivo lógico programable complejo consta de un grupo de bloques funcionales (bloques funcionales) programables. Las entradas y salidas de estos bloques funcionales están conectadas entre sí mediante una GIM (matriz de interconexión global). Esta matriz de interconexión es reconfigurable, por lo que podemos modificar los contactos entre los bloques funcionales. Habrá algunos bloques de entrada y salida que nos permitirán unir CPLD al mundo externo. La arquitectura de CPLD se muestra a continuación.

Generalmente, el FB programable se parece al matriz de puertas lógicas , donde se puede programar una matriz de puertas AND y las puertas OR son estables. Pero, cada fabricante tiene su forma de pensar para diseñar el bloque funcional. Se puede encontrar un o / p listado operando las señales de retroalimentación obtenidas de las salidas de la puerta OR.

Arquitectura CPLD

En la programación de CPLD, el diseño se codifica primero en lenguaje Verilog o VHDL una vez que el código está (simulado y sintetizado. Durante la síntesis, el modelo CPLD (dispositivo de destino) se selecciona a mano y se produce una lista de redes de mapeo basada en tecnología. Esta lista puede estar cerca -Ajustar la arquitectura CPLD genuina utilizando un proceso de lugar y ruta, generalmente logrado por el software de lugar y ruta de propiedad de la empresa CPLD. Luego, el operador realizará algunos procesos de confirmación. Si todo está bien, utilizará el CPLD, de lo contrario él lo reorganizará.

Problemas de arquitectura de CPLD

Al considerar un dispositivo lógico programable complejo para su uso en el diseño, se pueden tener en cuenta algunos problemas de arquitectura siguientes

- La tecnología de programación

- La capacidad del bloque de funciones

- La capacidad de E / S

Algunas de las familias de CPLD de diferentes minoristas incluyen

- Familias Altera MAX 7000 y MAX 9000

- Familias de ATF y ATV de Atmel

- Lattice isp familia LSI

- Lattice (Vantis) familia MACH

- Familia Xilinx XC9500

Familias de CPLD

Aplicaciones de CPLD

Las aplicaciones de las CPLD incluyen las siguientes

- Los dispositivos lógicos programables complejos son ideales para aplicaciones de control críticas de alto rendimiento.

- CPLD se puede utilizar en diseños digitales para realizar las funciones de cargador de arranque

- CPLD se utiliza para cargar los datos de configuración de una matriz de puertas programables en campo desde la memoria no volátil.

- Generalmente, se utilizan en aplicaciones de diseño pequeño como la decodificación de direcciones.

- Los CPLD se utilizan con frecuencia en muchas aplicaciones, como en dispositivos portátiles que funcionan con baterías y sensibles a los costos, debido a su bajo tamaño y uso de baja energía.

Por lo tanto, se trata de una arquitectura compleja de dispositivos lógicos programables y sus aplicaciones. Esperamos que comprenda mejor este concepto. Además, cualquier consulta sobre este concepto o para implementar cualquier proyecto eléctrico y electrónico , dé sus valiosas sugerencias comentando en la sección de comentarios a continuación. Aquí hay una pregunta para usted, ¿cuál es la diferencia entre CPLD y FPGA?

Créditos fotográficos:

- CPLD wikimedia

- Arquitectura de CPLD slidesharecdn