Hubo una época en la que las computadoras tenían un tamaño gigantesco que para instalarlas se requería fácilmente un espacio en la habitación. Pero hoy están tan evolucionados que incluso podemos llevarlos como cuadernos fácilmente. La innovación que lo hizo posible fue el concepto de Circuitos Integrados. En Circuitos integrados , un gran número de activos y elementos pasivos junto con sus interconexiones se desarrollan sobre una pequeña oblea de silicio típicamente de 50 por 50 milésimas de pulgada en sección transversal. Los procesos básicos seguidos para la producción de tales circuitos incluyen crecimiento epitaxial, difusión de impurezas enmascaradas, crecimiento de óxido y grabado con óxido, utilizando fotolitografía para hacer patrones.

Los componentes sobre la oblea incluyen resistencias, transistores, diodos, capacitores, etc. El elemento más complicado de fabricar sobre los IC son los transistores. Los transistores son de varios tipos como CMOS, BJT, FET. Elegimos el tipo de tecnología de transistores que se implementará sobre un IC en función de los requisitos. En este artículo vamos a familiarizarnos con el concepto de Fabricación CMOS (o) fabricación de transistores como CMOS.

Fabricación CMOS

Para menos requisitos de disipación de energía Tecnología CMOS se utiliza para implementar transistores. Si necesitamos un circuito más rápido, los transistores se implementan sobre IC usando BJT . Fabricación de Transistores CMOS ya que los CI se pueden hacer de tres métodos diferentes.

La tecnología N-well / P-well, donde la difusión de tipo n se realiza sobre un sustrato de tipo p o la difusión de tipo p se realiza sobre un sustrato de tipo n, respectivamente.

los Tecnología de pozo doble , dónde NMOS y transistor PMOS se desarrollan sobre la oblea por difusión simultánea sobre una base de crecimiento epitaxial, en lugar de un sustrato.

El proceso de silicio sobre aislante, en el que, en lugar de utilizar silicio como sustrato, se utiliza un material aislante para mejorar la velocidad y la susceptibilidad al enganche.

Tecnología N- well / P- well

CMOS se puede obtener integrando ambos Transistores NMOS y PMOS sobre la misma oblea de silicio. En la tecnología de pozos N, un pozo de tipo n se difunde sobre un sustrato de tipo p, mientras que en el pozo P es al revés.

Pasos de fabricación CMOS

los Proceso de fabricación CMOS fluir se lleva a cabo utilizando veinte pasos básicos de fabricación mientras se fabrica utilizando tecnología de pozos N / pozos P.

Haciendo CMOS usando N well

Paso 1: Primero elegimos un sustrato como base para la fabricación. Para el pozo N, se selecciona un sustrato de silicio de tipo P.

Sustrato

Paso 2 - Oxidación: La difusión selectiva de impurezas de tipo n se logra utilizando SiO2 como barrera que protege partes de la oblea contra la contaminación del sustrato. SiO2se establece mediante un proceso de oxidación que se realiza exponiendo el sustrato a oxígeno e hidrógeno de alta calidad en una cámara de oxidación a aproximadamente 10000c

Oxidación

Paso 3 - Crecimiento de fotorresistencia: En esta etapa para permitir el grabado selectivo, la capa de SiO2 se somete al proceso de fotolitografía. En este proceso, la oblea se recubre con una película uniforme de una emulsión fotosensible.

Crecimiento de fotorresistencia

Paso 4 - Enmascaramiento: Este paso es la continuación del proceso de fotolitografía. En este paso, se hace un patrón de apertura deseado usando una plantilla. Esta plantilla se utiliza como máscara sobre el fotorresistente. El sustrato ahora está expuesto a Rayos uv el fotorresistente presente debajo de las regiones expuestas de la máscara se polimeriza.

Enmascaramiento de fotorresistencia

Paso 5 - Eliminación de fotorresistente no expuesto: Se quita la máscara y la región no expuesta de fotorresistente se disuelve revelando la oblea usando un producto químico como el tricloroetileno.

Eliminación de fotorresistente

Paso 6 - Grabado: La oblea se sumerge en una solución de grabado de ácido fluorhídrico, que elimina el óxido de las áreas a través de las cuales se difundirán los dopantes.

Grabado de SiO2

Paso 7: eliminación de toda la capa fotorresistente: Durante el proceso de grabado , las porciones de SiO2 que están protegidas por la capa fotorresistente no se ven afectadas. La máscara fotorresistente se quita ahora con un disolvente químico (H2SO4 caliente).

Eliminación de la capa fotorresistente

Paso 8 - Formación del pozo N: Las impurezas de tipo n se difunden en el sustrato de tipo p a través de la región expuesta formando así un pozo N-.

Formación de N-well

Paso 9 - Eliminación de SiO2: La capa de SiO2 ahora se elimina usando ácido fluorhídrico.

Eliminación de SiO2

Paso 10 - Deposición de polisilicio: La desalineación de la puerta de un Transistor CMOS conduciría a la capacitancia no deseada que podría dañar el circuito. Por lo tanto, para evitar este 'proceso de puerta autoalineada', se prefiere cuando las regiones de puerta se forman antes de la formación de la fuente y el drenaje mediante la implantación de iones.

Deposición de polisilicio

El polisilicio se utiliza para la formación de la puerta porque puede soportar altas temperaturas superiores a 8000.0c cuando una oblea se somete a métodos de recocido para la formación de fuente y drenaje. El polisilicio se deposita usando Proceso de deposición química sobre una fina capa de óxido de puerta. Este óxido de puerta delgado debajo de la capa de polisilicio evita más dopaje debajo de la región de la puerta.

Paso 11 - Formación de la región de la puerta: Excepto las dos regiones necesarias para la formación de la puerta para Transistores NMOS y PMOS la porción restante de polisilicio se elimina.

Formación de la región de la puerta

Paso 12 - Proceso de oxidación: Se deposita una capa de oxidación sobre la oblea que actúa como un escudo para más procesos de difusión y metalización .

Proceso de oxidación

Paso 13 - Enmascaramiento y difusión: Para hacer regiones para la difusión de impurezas de tipo n usando un proceso de enmascaramiento, se hacen pequeños huecos.

Enmascaramiento

Mediante el proceso de difusión se desarrollan tres regiones n + para la formación de terminales de NMOS.

N-difusión

Paso 14 - Eliminación de óxido: Se quita la capa de óxido.

Eliminación de óxido

Paso 15 - Difusión tipo P: Similar a la difusión de tipo n para formar los terminales de PMOS se llevan a cabo difusión de tipo p.

Difusión tipo P

Paso 16 - Colocación de óxido de campo grueso: Antes de formar los terminales de metal, se coloca un óxido de campo grueso para formar una capa protectora para las regiones de la oblea donde no se requieren terminales.

Capa de óxido de campo grueso

Paso 17 - Metalización: Este paso se utiliza para la formación de terminales de metal que pueden proporcionar interconexiones. El aluminio se extiende por toda la oblea.

Metalización

Paso 18 - Eliminación del exceso de metal: El exceso de metal se elimina de la oblea.

Paso 19 - Formación de terminales: En los espacios formados después de la eliminación del exceso de metal, se forman terminales para las interconexiones.

Formación de terminales

Paso 20 - Asignación de nombres de terminales: Los nombres se asignan a las terminales de Transistores NMOS y PMOS .

Asignar nombres de terminales

Fabricación de CMOS utilizando tecnología de pozo P

El proceso de pozos p es similar al proceso de pozos N excepto que aquí se usa un sustrato de tipo n y se llevan a cabo difusiones de tipo p. Normalmente, por simplicidad, se prefiere el proceso de N pozos.

Fabricación de tubos gemelos de CMOS

Utilizando el proceso de doble tubo, se puede controlar la ganancia de los dispositivos de tipo P y N. Varios pasos involucrados en el fabricación de CMOS utilizando el método de tubo doble son como sigue

- Se toma un sustrato de tipo no p ligeramente dopado y se usa la capa epitaxial. La capa epitaxial protege el problema de enganche en el chip.

- Se cultivan las capas de silicio de alta pureza con espesor medido y concentración exacta de dopante.

- Formación de tubos para pozos P y N.

- Construcción de óxido delgado para protección contra la contaminación durante los procesos de difusión.

- La fuente y el drenaje se forman utilizando métodos de implantación de iones.

- Los cortes están hechos para hacer porciones para contactos metálicos.

- La metalización se realiza para dibujar contactos metálicos.

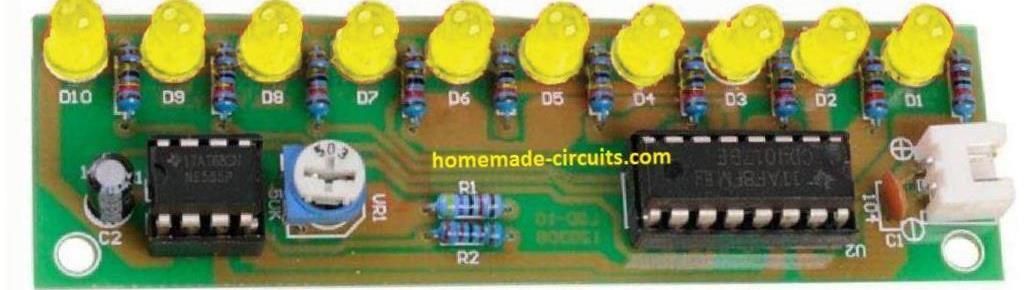

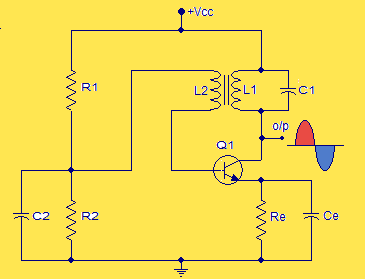

Diseño de IC CMOS

La vista superior de a CMOS fabricación y diseño es dado. Aquí se pueden ver claramente varios contactos de metal y difusiones de N pozos.

Diseño de IC CMOS

Por lo tanto, se trata de Técnicas de fabricación CMOS . Consideremos una oblea de 1 en cuadrado dividida en 400 astillas de área de superficie de 50 mil por 50 milésimas de pulgada. Se necesita un área de 50 mil2 para fabricar un transistor. Por lo tanto, cada IC contiene 2 transistores, por lo que hay 2 x 400 = 800 transistores construidos en cada oblea. Si se procesan 10 obleas por lote, entonces se pueden fabricar 8000 transistores simultáneamente. ¿Cuáles son los diversos componentes que ha observado en un CI?