Dos tipos principales de FET que existen actualmente son: JFET y MOSFET.

Los MOSFET se pueden clasificar además en tipo de agotamiento y tipo de mejora. Ambos tipos definen el modo fundamental de funcionamiento de los MOSFET, mientras que el término MOSFET en sí es la abreviatura de transistor de efecto de campo de semiconductor de óxido metálico.

Debido a que los dos tipos tienen diferentes características de funcionamiento, evaluaremos cada uno de ellos por separado en diferentes artículos.

Diferencia entre MOSFET de mejora y agotamiento

Básicamente, a diferencia de los MOSFET de mejora, los MOSFET de agotamiento están en estado activado incluso en presencia de 0 V a través de los terminales de puerta a fuente (VGS).

Para un MOSFET de mejora, el voltaje de puerta a fuente (VGS) debe estar por encima de su voltaje umbral de puerta a fuente (VGS (th)) para hacer que conduzca .

Sin embargo, para un MOSFET de agotamiento de canal N, su valor VGS (th) está por encima de 0 V. Esto significa que incluso si VGS = 0 V, un MOSFET de agotamiento puede conducir corriente. Para apagarlo, el VGS de un MOSFET de agotamiento debe reducirse por debajo del VGS (th) (negativo).

En este artículo, discutiremos el tipo de agotamiento MOSFET, que se dice que tiene características que coinciden con las de un JFET. La similitud está entre el corte y la saturación cerca de IDSS.

Construcción básica

La figura 5.23 muestra la estructura interna básica de un MOSFET de tipo empobrecimiento de canal n.

Podemos encontrar un bloque de material tipo p creado a partir de una base de silicona. Este bloque se llama sustrato.

El sustrato es la base o cimiento sobre el que se construye un MOSFET. Para algunos MOSFET, está vinculado internamente con la terminal 'fuente'. Además, muchos dispositivos ofrecen una salida adicional en forma de SS, con un MOSFET de 4 terminales, como se muestra en la figura 5.23.

El drenaje y los terminales de la fuente se conectan a través de contactos conductores a ubicaciones con n dopados y se conectan a través de un canal n, como se indica en la misma figura.

La puerta también está conectada a una capa metálica, aunque está aislada del canal n a través de una fina capa de dióxido de silicio (SiO2).

SiO2posee una forma única de propiedad de aislamiento llamada dieléctrico que crea un campo eléctrico opuesto dentro de sí mismo en respuesta a un campo eléctrico aplicado externamente.

Al ser una capa aislante, el material SiO2nos ofrece la siguiente información importante:

Se desarrolla un aislamiento completo entre el terminal de la puerta y el canal mosfet con este material.

Además, es debido al SiO2, la puerta del mosfet puede presentar un grado extremadamente alto de impedancia de entrada.

Debido a esta propiedad vital de alta impedancia de entrada, la corriente de puerta IGRAMOes virtualmente cero amperios para cualquier configuración MOSFET polarizada en CC.

Operación básica y características

Como se puede ver en la figura 5.24, la puerta a voltaje de la fuente se ha configurado a cero voltios conectando los dos terminales juntos, mientras que un voltaje VDSse aplica a través de los terminales de drenaje y fuente.

Con la configuración anterior, el lado de drenaje establece un potencial positivo por los electrones libres del canal n, junto con una corriente equivalente a través del canal JFET. Además, la corriente resultante VGS= 0V todavía se identifica como IDSS, como se muestra en la figura 5.25

Podemos ver que en la figura 5.26 el voltaje de fuente de puerta VGSrecibe un potencial negativo en forma de -1V.

Este potencial negativo intenta forzar a los electrones hacia el sustrato del canal p (ya que las cargas se repelen) y extrae los agujeros del sustrato del canal p (ya que las cargas opuestas se atraen).

Dependiendo de cuán grande sea este sesgo negativo VGSes decir, tiene lugar una recombinación de huecos y electrones que da como resultado la reducción de electrones libres en el canal n disponible para la conducción. Los niveles más altos de sesgo negativo dan como resultado una mayor tasa de recombinación.

En consecuencia, la corriente de drenaje se reduce a medida que aumenta la condición de polarización negativa anterior, lo que se demuestra en la figura 5.25 para VGSniveles de VGS= -1, -2 y así sucesivamente, hasta la marca de pellizco de -6V.

Como resultado, la corriente de drenaje, junto con la gráfica de la curva de transferencia, procede como la de un JFET.

Ahora, para la V positivaGSvalores, la puerta positiva atraerá el exceso de electrones (portadores libres) del sustrato tipo p, debido a la corriente de fuga inversa. Esto establecerá nuevos portadores mediante las colisiones resultantes entre las partículas en aceleración.

Como el voltaje de puerta a fuente tiende a aumentar a una tasa positiva, la corriente de drenaje muestra un aumento rápido, como se demuestra en la figura 5.25 por las mismas razones que se discutieron anteriormente.

La brecha desarrollada entre las curvas de VGS= 0V y VGS= +1 muestra claramente la cantidad por la cual la corriente aumentó debido a la variación de 1 - V de la VGS

Debido al rápido aumento de la corriente de drenaje, debemos tener cuidado con la clasificación de corriente máxima, de lo contrario, podría cruzar el límite de voltaje de puerta positivo.

Por ejemplo, para el tipo de dispositivo representado en la figura 5.25, aplicando un VGS= + 4V haría que la corriente de drenaje aumente a 22.2 mA, lo que puede estar cruzando el límite máximo de ruptura (corriente) del dispositivo.

La condición anterior muestra que el uso de un voltaje de puerta a fuente positivo genera un efecto mejorado sobre la cantidad de portadores libres en el canal, en contraposición a cuando VGS= 0V.

Esta es la razón por la que la región de voltaje de puerta positiva en las características de drenaje o transferencia se conoce generalmente como región de mejora . Esta región se encuentra entre el límite y el nivel de saturación de IDSSo la región de agotamiento.

Resolver un problema de ejemplo

Ventajas y aplicaciones

A diferencia de los MOSFET en modo de mejora, donde encontramos que la corriente de drenaje cae a cero en respuesta a un voltaje de puerta a fuente cero, el FET moderno en modo de agotamiento presenta una corriente notable con voltaje de puerta cero. Para ser precisos, la resistencia de drenaje a fuente suele ser de 100 ohmios en voltaje cero.

Como se indica en el gráfico anterior, los rds de resistencia ON(en)vs rango de señal analógica parece una respuesta prácticamente plana. Esta característica, junto con los niveles de baja capacitancia de estos dispositivos de tipo de agotamiento avanzado, les permite ser específicamente ideales como interruptores analógicos para aplicaciones de conmutación de audio y video.

El atributo 'normalmente encendido' del MOSFET en modo de agotamiento permite que el dispositivo sea perfectamente adecuado para reguladores de corriente FET individuales.

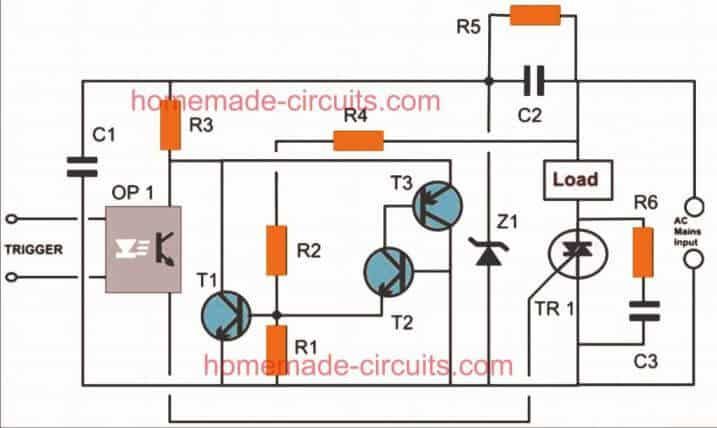

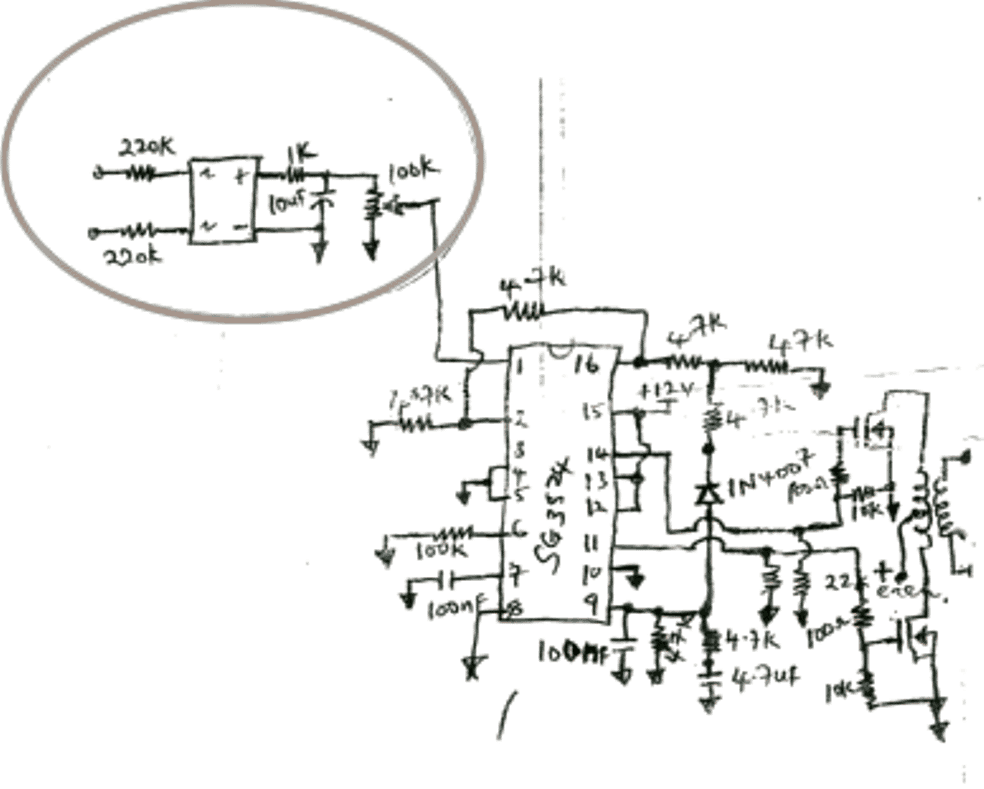

En la siguiente figura se puede ver un circuito de ejemplo.

El valor de Rs se puede determinar mediante la fórmula:

Rs= VGSapagado[1 - (yoD/IDSS)1/2] / ID

dónde ID es la cantidad de corriente regulada requerida en la salida.

La principal ventaja de los MOSFET en modo de agotamiento en aplicaciones de fuente de corriente es su capacitancia de drenaje mínima, que los hace apropiados para aplicaciones de polarización en circuitos de baja fuga de entrada y velocidad media (> 50 V / us).

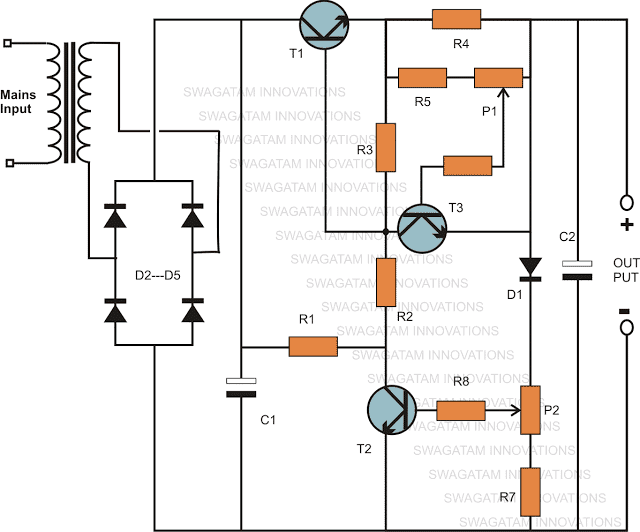

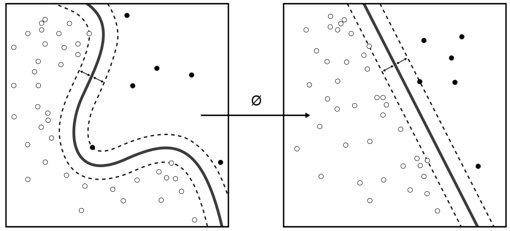

La siguiente figura muestra un diferencial frontal de corriente de fuga de entrada baja utilizando una función FET doble de fuga baja.

En términos generales, cualquier lado del JFET estará sesgado en ID = 500 uA. Por lo tanto, la corriente que se puede obtener para la compensación de carga y las capacitancias parásitas se restringe a 2ID o, en casos como este, a 1,0 mA. Las características correspondientes del JFET están probadas en producción y aseguradas en la hoja de datos.

Cs simboliza la capacitancia de salida de la fuente de corriente 'cola' de la etapa de entrada. Esta capacitancia es crucial en amplificadores no inversores, debido al hecho de que la etapa de entrada experimenta intercambios de señal significativos a través de esta red, y las corrientes de carga en Cs podrían ser grandes. En caso de que se empleen fuentes de corriente normales, esta capacitancia de cola podría ser responsable del deterioro notable de la velocidad de respuesta en circuitos no inversores (en comparación con las aplicaciones inversoras, donde las corrientes de carga en Cs tienden a ser mínimas).

La caída en la tasa de respuesta podría expresarse como:

1 / 1+ (Cs / Sc)

Siempre que Cs sea menor que Cc (el condensador de compensación), es posible que apenas haya variación en la velocidad de respuesta. Al trabajar con DMOS FET, Cs puede rondar los 2 pF. Esta estrategia produce una gran mejora en la velocidad de respuesta. Cuando se necesiten déficits de corriente superiores a 1 a 5 mA, el dispositivo podría polarizarse en el modo de mejora para generar hasta 20 mA para un VGS máximo de +2,5 V, con una capacitancia de salida mínima que sigue siendo un aspecto clave.

La siguiente aplicación muestra un circuito de fuente de corriente en modo de mejora adecuado.

Se podría construir un interruptor analógico 'normalmente encendido' para los requisitos en los que la condición estándar se vuelve necesaria durante una falla de voltaje de suministro, por ejemplo, en el rango automático de herramientas de prueba o para asegurar el arranque preciso de los circuitos lógicos en el encendido.

El voltaje de umbral negativo reducido del dispositivo ofrece prerrequisitos básicos de accionamiento y permite trabajar con un voltaje mínimo.

El circuito a continuación demuestra los factores de polarización comunes para cualquier conmutador analógico DMOS en modo de agotamiento.

Para hacer que el dispositivo se apague, es necesario un voltaje negativo en la puerta. Habiendo dicho eso, la resistencia activa podría minimizarse cuando el FET se mejora adicionalmente usando un voltaje de puerta positivo, habilitándolo específicamente en la región del modo de mejora junto con la región del modo de agotamiento.

Esta respuesta se puede ver en el siguiente gráfico.

La ganancia de alta frecuencia de la unidad, junto con sus bajos valores de capacitancia, ofrece una mayor 'figura de mérito'. Es realmente un elemento crucial en la amplificación de VHF y UHF, que especifica el producto de ancho de banda de ganancia (GBW) del FET, que podría describirse como:

GBW = gfs / 2 Pi (Cen+ Cfuera)

MOSFET de tipo de agotamiento de canal p

La construcción de un MOSFET de tipo empobrecimiento de canal p es un reverso perfecto de una versión de canal n que se muestra en la figura 5.23. Es decir, el sustrato ahora toma la forma de un tipo ny el canal se convierte en un tipo p, como se puede ver en la figura 5.28a a continuación.

La identificación del terminal permanece sin cambios, pero la tensión y la polaridad de la corriente se invierten, como se indica en la misma figura. Las características del drenaje serían exactamente como se muestra en la figura 5.25, excepto que VDSsigno que en este caso obtendrá un valor negativo.

La corriente de drenaje IDmuestra una polaridad positiva también en este caso, eso es porque ya hemos invertido su dirección. VGSmuestra una polaridad opuesta, lo cual es comprensible, como se indica en la figura 5.28c.

Porque VGSse invierte produce una imagen de espejo para las características de transferencia como se indica en la figura 5,28b.

Es decir, la corriente de drenaje aumenta en V positivoGSregión desde el punto de corte en VGS= Vp hasta queDSS, luego continúa aumentando a medida que el valor negativo de VGSsube.

Simbolos

Los signos gráficos de un MOSFET de tipo de agotamiento de canales ny p se pueden observar en la figura 5.29 anterior.

Observe la forma en que los símbolos seleccionados pretenden representar la verdadera estructura del dispositivo.

La ausencia de una interconexión directa (debido al aislamiento de la puerta) entre la puerta y el canal está simbolizada por un espacio entre la puerta y los diferentes terminales del símbolo.

La línea vertical que representa el canal está unida entre el drenaje y la fuente y está “sujeta” por el sustrato.

En la figura anterior se proporcionan dos grupos de símbolos para cada tipo de canal para resaltar el hecho de que en algunos dispositivos el sustrato puede ser accesible desde el exterior, mientras que en otros es posible que no se vea.

MOSFET (tipo de mejora)

Aunque los MOSFET de tipo de reducción y de mejora tienen un aspecto similar con sus estructuras internas y modo funcional, sus características pueden ser bastante diferentes.

La principal diferencia es la corriente de drenaje, que depende de un nivel específico de voltaje de puerta a fuente para la acción de corte.

Precisamente, un MOSFET de tipo de mejora de canal n puede funcionar con un voltaje de puerta / fuente positivo, en lugar de un rango de potenciales negativos que normalmente pueden afectar un MOSFET de tipo de agotamiento.

Construcción básica

Puede visualizar el MOSFET de tipo de mejora de canal n en la siguiente

Figura 5.31.

Se crea una sección de material de tipo p a través de una base de silicio y, como se aprendió antes, se denomina sustrato.

En algunas ocasiones, este sustrato se adjunta internamente con el pin de origen en un MOSFET de tipo de agotamiento, mientras que en algunos casos se termina como un cuarto cable para permitir un control externo de su nivel de potencial.

Los terminales de fuente y drenaje se unen, como de costumbre, mediante contactos metálicos a regiones dopadas con n.

Sin embargo, puede ser importante visualizar que en la figura 5.31 falta el canal entre las dos regiones dopadas con n.

Esto puede considerarse como la diferencia fundamental entre el diseño interno de un MOSFET de tipo de reducción y de tipo de mejora, es decir, la ausencia de un canal inherente que se supone que es parte del dispositivo.

La capa de SiO2 aún prevalece, lo que asegura un aislamiento entre la base metálica del terminal de la puerta y la región entre el drenaje y la fuente. Sin embargo, aquí se puede ver de pie separado de la sección de material de tipo p.

De la discusión anterior podemos concluir que un diseño interno de MOSFET de mejora y agotamiento puede tener algunas similitudes, excepto el canal que falta entre drenaje / fuente para un tipo de mejora de MOSFET.

Operación básica y características

Para un MOSFET de tipo de mejora, cuando se introduce un 0 V en su VGS, debido a que falta el canal n (que se sabe que lleva muchos portadores libres), la salida de corriente es cero, lo cual es bastante diferente al tipo de agotamiento. de MOSFET, teniendo ID = IDSS.

En tal situación debido a una ruta faltante a través de los terminales de drenaje / fuente, grandes cantidades de portadores en forma de electrones no pueden acumularse en el drenaje / fuente (debido a las regiones dopadas con n).

Aplicando algún potencial positivo en VDS, con VGS ajustado a cero voltios y el terminal SS en cortocircuito con el terminal de origen, en realidad encontramos un par de uniones pn polarizadas inversamente entre las regiones n-dopadas y el sustrato p para permitir cualquier conducción notable a través drenar a la fuente.

En la figura 5.32 se muestra una condición en la que se aplican VDS y VGS con un voltaje positivo superior a 0 V, lo que permite que el drenaje y la compuerta tengan un potencial positivo con respecto a la fuente.

El potencial positivo en la puerta empuja los agujeros en el sustrato p a lo largo del borde de la capa de SiO2 saliendo de la ubicación y entrando más profundamente en las regiones del sustrato p, como se muestra en la figura anterior. Esto sucede debido a cargas similares que se repelen entre sí.

Esto da como resultado una región de agotamiento que se crea cerca de la capa aislante de SiO2 que no tiene agujeros.

A pesar de esto, los electrones del sustrato p, que son los portadores minoritarios del material, son empujados hacia la puerta positiva y comienzan a reunirse en la región cercana a la superficie de la capa de SiO2.

Debido a la propiedad de aislamiento de la capa de SiO2, los portadores negativos permiten que los portadores negativos sean absorbidos en el terminal de la puerta.

A medida que aumentamos el nivel de VGS, la densidad de electrones cerca de la superficie de SiO2 también aumenta, hasta que finalmente la región inducida de tipo n puede permitir una conducción cuantificable a través del drenaje / fuente.

La magnitud de VGS que causa un aumento óptimo en la corriente de drenaje se denomina voltaje umbral, representado por el símbolo VT . En las hojas de datos, podrá ver esto como VGS (Th).

Como se aprendió anteriormente, debido a la ausencia de un canal en VGS = 0, y 'mejorado' con la aplicación de voltaje positivo de puerta a fuente, este tipo de MOSFET se conocen como MOSFET de tipo de mejora.

Encontrará que los MOSFET de tipo de mejora y de agotamiento exhiben regiones de tipo de mejora, pero el término mejora se usa para este último porque funciona específicamente usando un modo de operación de mejora.

Ahora, cuando VGS se empuja por encima del valor umbral, la concentración de portadores libres aumentará en el canal donde se induce. Esto hace que aumente la corriente de drenaje.

Por otro lado, si mantenemos el VGS constante y aumentamos el nivel de VDS (voltaje de drenaje a fuente), esto finalmente hará que el MOSFET alcance su punto de saturación, como normalmente también sucedería con cualquier JFET o MOSFET de agotamiento.

Como se muestra en la figura 5.33, la ID de la corriente de drenaje se nivela con la ayuda de un proceso de pellizco, indicado por el canal más estrecho hacia el extremo de drenaje del canal inducido.

Al aplicar la ley de voltaje de Kirchhoff a los voltajes terminales del MOSFET en la figura 5.33, obtenemos:

Si VGS se mantiene constante a un valor específico, por ejemplo 8 V, y VDS se eleva de 2 a 5 V, el voltaje VDG por Eq. Se puede ver que 5.11 cae de -6 a -3 V, y el potencial de la puerta se vuelve cada vez menos positivo con respecto al voltaje de drenaje.

Esta respuesta prohíbe que los electrones o portadores libres sean atraídos hacia esta región del canal inducido, lo que a su vez da como resultado una caída en el ancho efectivo del canal.

En última instancia, el ancho del canal disminuye hasta el punto de pellizcar, alcanzando una condición de saturación similar a lo que ya aprendimos en nuestro artículo anterior sobre MOSFET de agotamiento.

Es decir, aumentar aún más el VDS con un VGS fijo no afecta el nivel de saturación de ID, hasta el punto en que se alcanza una situación de avería.

Observando la figura 5.34 podemos identificar que para un MOSFET como en la figura 5.33 que tiene VGS = 8 V, la saturación tiene lugar a un nivel de VDS de 6 V.Para ser precisos, el nivel de saturación de VDS está asociado al nivel de VGS aplicado por:

Sin duda, esto implica que cuando el valor de VT es fijo, aumentar el nivel de VGS causará proporcionalmente niveles más altos de saturación para VDS a través del locus de los niveles de saturación.

En referencia a las características que se muestran en la figura anterior, el nivel de TT es de 2 V, lo cual es evidente por el hecho de que la corriente de drenaje ha caído a 0 mA.

Por lo tanto, normalmente podemos decir:

Cuando los valores de VGS son menores que el nivel de umbral para el MOSFET de tipo mejora, su corriente de drenaje es 0 mA.

También podemos ver claramente en la figura anterior que siempre que el VGS se eleve más alto de VT a 8 V, el nivel de saturación correspondiente para ID también aumenta de 0 a 10 mA.

Además, podemos notar que el espacio entre los niveles de VGS aumenta con un aumento en el valor de VGS, lo que provoca incrementos infinitamente crecientes en la corriente de drenaje.

Encontramos que el valor de la corriente de drenaje está relacionado con el voltaje de puerta a fuente para niveles de VGS que son mayores que VT, a través de la siguiente relación no lineal:

El término que se muestra entre corchetes es el término responsable de la relación no lineal entre ID y VGS.

El término k es una constante y es una función del diseño MOSFET.

Podemos averiguar el valor de esta constante k mediante la siguiente ecuación:

donde ID (activado) y VGD (activado) son valores que dependen específicamente de la característica del dispositivo.

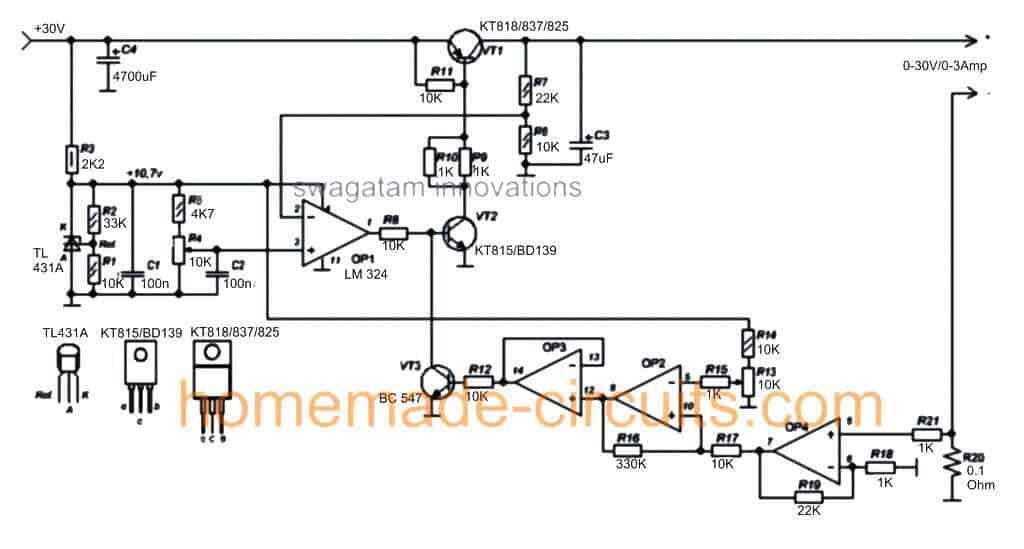

En la siguiente Fig. 5.35 a continuación, encontramos que las características de drenaje y transferencia están dispuestas una al lado de la otra para aclarar el proceso de transferencia entre sí.

Básicamente, es similar al proceso explicado anteriormente para JFET y MOSFET de agotamiento.

Sin embargo, para el presente caso debemos recordar que la corriente de drenaje es 0 mA para VGS VT.

Aquí, el ID puede ver una cantidad notable de corriente, que aumentará según lo determine la Ec. 5.13.

Tenga en cuenta que, al definir los puntos sobre las características de transferencia de las características del drenaje, solo consideramos los niveles de saturación. Esto restringe la región de operación a valores VDS más altos que los niveles de saturación establecidos por la Ec. (5.12).

MOSFET de tipo de mejora de canal p

La estructura de un MOSFET de tipo de mejora de canal p como se muestra en la Fig. 5.37a es justamente la opuesta a la que se muestra en la Fig. 5.31.

Es decir, ahora encontrará que un sustrato de tipo ny regiones dopadas con p debajo de las juntas de drenaje y fuente.

Los terminales siguen siendo los establecidos, pero cada una de las direcciones de la corriente y las polaridades de la tensión se invierten.

Las características de drenaje pueden verse como las que se muestran en la figura 5.37c, con cantidades crecientes de corriente causadas por magnitudes continuamente más negativas de VGS.

Las características de transferencia serían la impresión de espejo (alrededor del eje ID) de la curva de transferencia de la figura 5.35, con ID aumentando con valores cada vez más negativos de VGS por encima de VT, como se muestra en la figura 5.37b. Las ecuaciones (5.11) a (5.14) son igualmente apropiadas para los dispositivos de canal p.

Referencias:

- https://en.wikipedia.org/wiki/MOSFET

- https://hi.wikipedia.org/wiki/%E0%A4%AE%E0%A5%89%E0%A4%B8%E0%A4%AB%E0%A5%87%E0%A4%9F

Anterior: Circuito detector de RF antiespía - Detector de errores inalámbrico Siguiente: Características de transferencia