El transistor MOS es el elemento más fundamental en el diseño de circuitos integrados a gran escala. Estos transistores generalmente se clasifican en dos tipos PMOS y NMOS. La combinación de transistores NMOS y PMOS se conoce como Transistores CMOS . Lo diferente puertas lógicas y otros dispositivos lógicos digitales que se implementen deben tener lógica PMOS. Esta tecnología es económica y tiene buena resistencia a las interferencias. Este artículo analiza uno de los tipos de transistores MOS como un transistor PMOS.

¿Qué es el transistor PMOS?

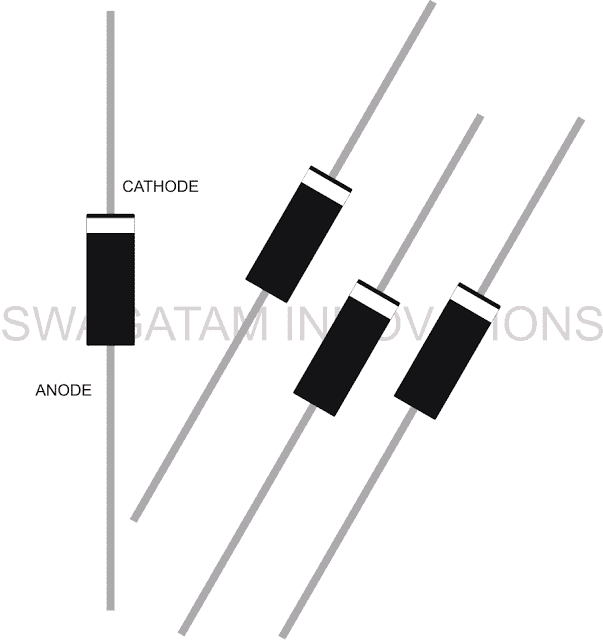

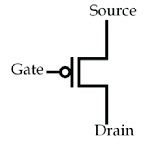

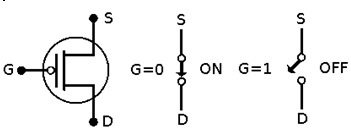

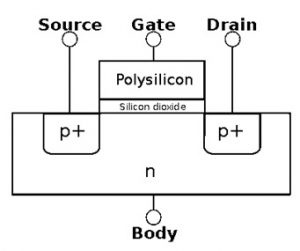

El transistor PMOS o semiconductor de óxido metálico de canal P es un tipo de transistor en el que los dopantes de tipo p se utilizan en la región del canal o de la puerta. Este transistor es exactamente el reverso del transistor NMOS. Estos transistores tienen tres terminales principales; la fuente, la puerta y el drenaje donde la fuente del transistor está diseñada con un sustrato de tipo p, y el terminal de drenaje está diseñado con un sustrato de tipo n. En este transistor, los portadores de carga como agujeros son responsables de la conducción de corriente. Los símbolos del transistor PMOS se muestran a continuación.

¿Cómo funciona el transistor PMOS?

El funcionamiento del transistor tipo p es bastante opuesto al del transistor tipo n. Este transistor formará un circuito abierto cada vez que obtenga un voltaje no despreciable, lo que significa que no hay flujo de electricidad desde la terminal de la puerta (G) a la fuente (S). De manera similar, este transistor forma un circuito cerrado cuando recibe un voltaje de alrededor de 0 voltios, lo que significa que la corriente fluye desde la terminal de la puerta (G) hacia el drenaje (D).

Esta burbuja también se conoce como burbuja de inversión. Entonces, la función principal de este círculo es invertir el valor del voltaje de entrada. Si el terminal de la puerta proporciona un voltaje de 1, entonces este inversor lo cambiará a cero y funcionará el circuito en consecuencia. Entonces, la función del transistor PMOS y el transistor NMOS es bastante opuesta. Una vez que los fusionemos en un solo circuito MOS, se convertirá en un circuito CMOS (semiconductor de óxido de metal complementario).

Sección transversal del transistor PMOS

La sección transversal del transistor PMOS se muestra a continuación. Un transistor pMOS se construye con un cuerpo de tipo n que incluye dos regiones de semiconductores de tipo p que están adyacentes a la puerta. Este transistor tiene una puerta de control como se muestra en el diagrama que controla el flujo de electrones entre los dos terminales como fuente y drenaje. En el transistor pMOS, el cuerpo se mantiene a un voltaje +ve. Una vez que el terminal de la puerta es positivo, los terminales de fuente y drenaje tienen polarización inversa. Una vez que esto sucede, no hay flujo de corriente, por lo que el transistor se apagará.

Una vez que se reduce el suministro de voltaje en el terminal de la puerta, los portadores de carga positiva serán atraídos hacia la parte inferior de la interfaz Si-SiO2. Siempre que el voltaje sea lo suficientemente bajo, el canal se invertirá y creará una vía conductora desde el terminal fuente hasta el drenaje al permitir el flujo de corriente.

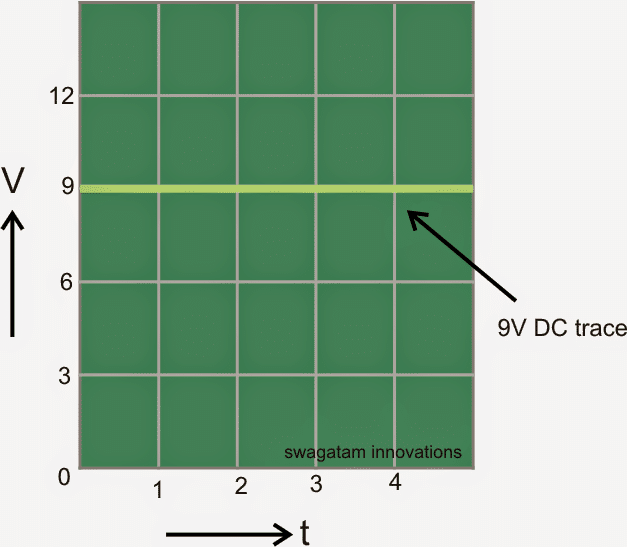

Cada vez que estos transistores se ocupan de la lógica digital, generalmente tienen dos valores diferentes solo como 1 y 0 (ENCENDIDO y APAGADO). El voltaje positivo del transistor se conoce como VDD, que representa el valor lógico alto (1) dentro de los circuitos digitales. Los niveles de voltaje VDD en Lógica TTL eran generalmente alrededor de 5V. En la actualidad, los transistores no pueden soportar voltajes tan altos porque normalmente oscilan entre 1,5 V y 3,3 V. El bajo voltaje se conoce frecuentemente como GND o VSS. Entonces, VSS significa la lógica '0' y también se establece normalmente en 0V.

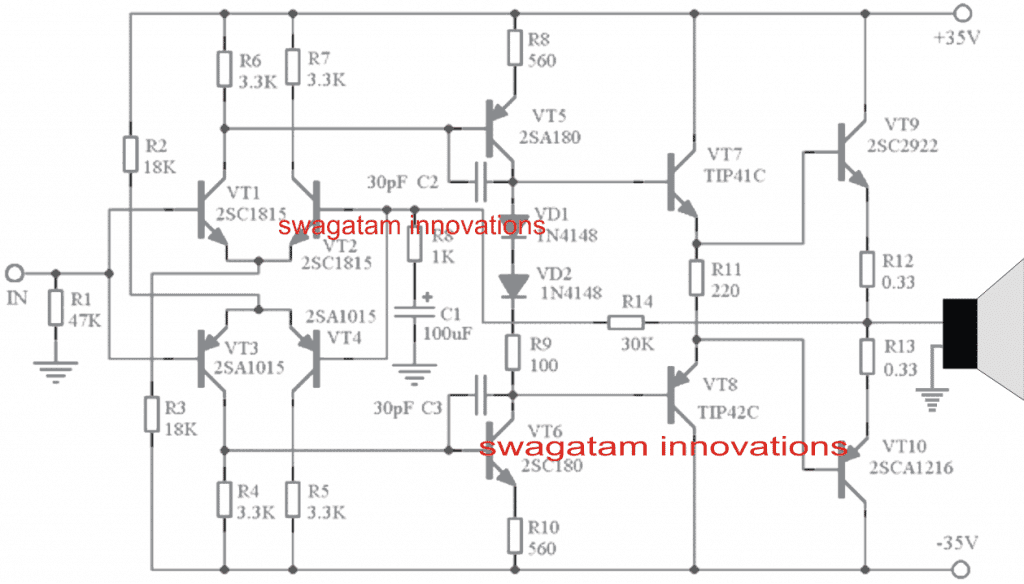

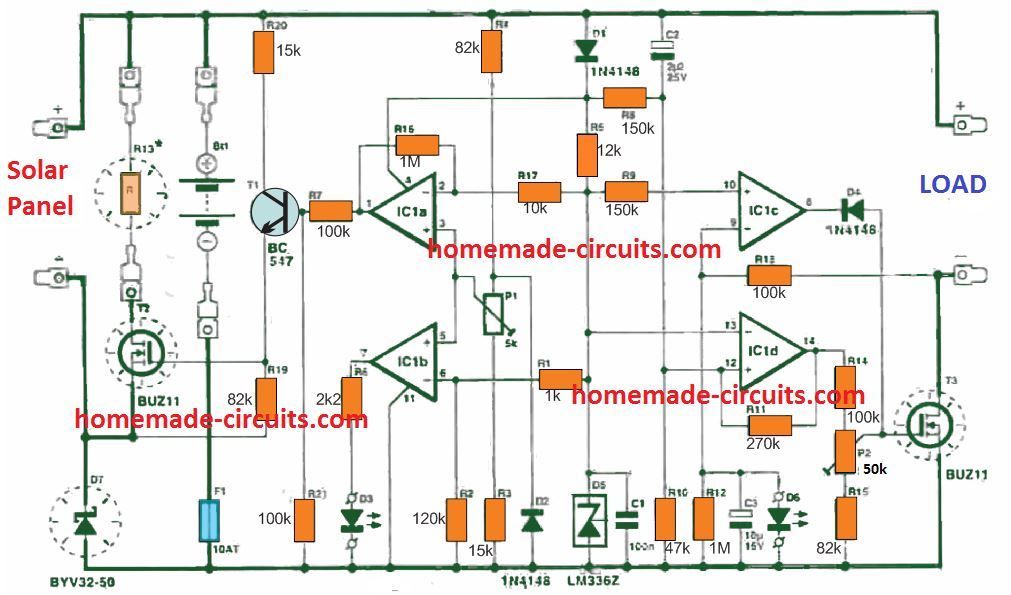

Circuito de transistores PMOS

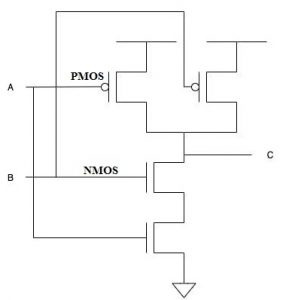

A continuación se muestra el diseño de la puerta NAND que utiliza el transistor PMOS y el transistor NMOS. En general, una puerta NAND en electrónica digital es una puerta lógica que también se denomina puerta NOT-AND. La salida de esta puerta es baja (0) solo si las dos entradas son altas (1) y su salida es un complemento de una puerta AND. Si alguna de las dos entradas es BAJA (0), entonces da resultados de salida altos.

En el siguiente circuito lógico, si la entrada A es 0 y B es 0, entonces una entrada de pMOS producirá '1' y una entrada de nMOS producirá '0'. Entonces, esta puerta lógica genera un '1' lógico porque está conectada a la fuente por un circuito cerrado y separada de GND por un circuito abierto.

Cuando A es '0' y B' es '1', entonces una entrada de pMOS generará un '1' y una entrada de NMOS generará un '0'. Por lo tanto, esta puerta producirá una puerta lógica porque está conectada a la fuente a través de un circuito cerrado y separada de GND por un circuito abierto. Cuando A es '1' y B es '0', entonces la entrada 'B' de pMOS generará una salida alta (1) y la entrada 'B' de NMOS generará una salida tan baja (0). Entonces, esta puerta lógica generará un 1 lógico porque está conectada a la fuente a través de un circuito cerrado y separada de GND por un circuito abierto.

Cuando A es '1' y B es '1', entonces una entrada de 'pMOS' producirá un cero, y una entrada de nMOS generará '1'. En consecuencia, también debemos verificar la entrada B de pMOS y nMOS. La entrada B de pMOS generará un '0' y la entrada B de nMOS generará un '1'. Entonces, esta puerta lógica generará un '0' lógico porque está separada de la fuente por un circuito abierto y está conectada a GND a través de un circuito cerrado.

Mesa de la verdad

La tabla de verdad del circuito lógico anterior se muestra a continuación.

|

A |

B |

C |

|

0 |

0 | 1 |

|

0 |

1 | 1 |

| 1 | 0 |

1 |

| 1 | 1 |

0 |

El voltaje de umbral del transistor PMOS es normalmente el 'Vgs', que es necesario para crear el canal conocido como inversión de canal. En un transistor PMOS, el sustrato y los terminales de origen simplemente se conectan a 'Vdd'. Si comenzamos a reducir el voltaje por referencia a la terminal de la fuente en la terminal de la puerta desde Vdd hasta un punto donde observe la inversión del canal, en esta posición si analiza que Vgs y la fuente están en el potencial alto, entonces obtendrá un valor negativo. Entonces, el transistor PMOS tiene un valor Vth negativo.

Proceso de fabricación de PMOS

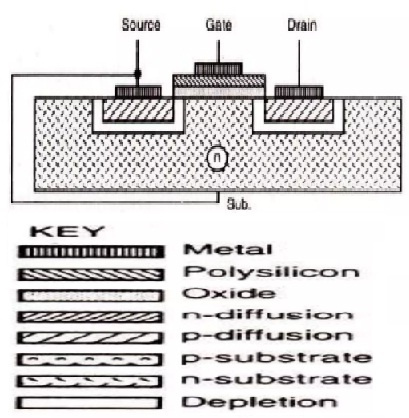

Los pasos involucrados en la fabricación de transistores PMOS se discuten a continuación.

Paso 1:

Una fina capa de oblea de silicio se convierte en material de tipo N simplemente dopando material de fósforo.

Paso 2:

Se cultiva una capa gruesa de dióxido de silicio (Sio2) sobre un sustrato de tipo p completo.

Paso 3:

Ahora la superficie está recubierta con una fotoprotección sobre la gruesa capa de dióxido de silicio.

Paso 4:

Después de eso, esta capa simplemente se expone a la luz ultravioleta a través de una máscara que define aquellas regiones en las que se llevará a cabo la difusión junto con los canales de transistores.

Paso 5:

Estas regiones se graban mutuamente con el dióxido de silicio subyacente para que la superficie de la oblea quede expuesta dentro de la ventana definida por la máscara.

Paso 6:

La fotoprotección restante se separa y la capa delgada de Sio2 crece típicamente 0,1 micrómetros sobre toda la superficie del chip. Después de eso, se coloca polisilicio sobre esto para formar la estructura de la puerta. Se coloca una fotoprotección sobre toda la capa de polisilicio y expone la luz ultravioleta a través de la máscara2.

Paso 7:

Las difusiones se logran mediante el calentamiento de la oblea a la temperatura máxima y el paso del gas con las impurezas de tipo p deseadas, como el boro.

Paso 8:

Se cultiva dióxido de silicio de 1 micrómetro de espesor y se deposita material fotorresistente sobre él. Exponga la luz ultravioleta con mask3 en las áreas preferidas de la compuerta, fuente y drenaje que están grabadas para hacer los cortes de contacto.

Paso 9:

Ahora se deposita un metal o aluminio sobre su superficie de 1 micrómetro de espesor. Una vez más, se cultiva un material fotorresistente por todo el metal y se expone a la luz ultravioleta a través de la máscara4, que se graba para formar el diseño de interconexión requerido. La estructura final de PMOS se muestra a continuación.

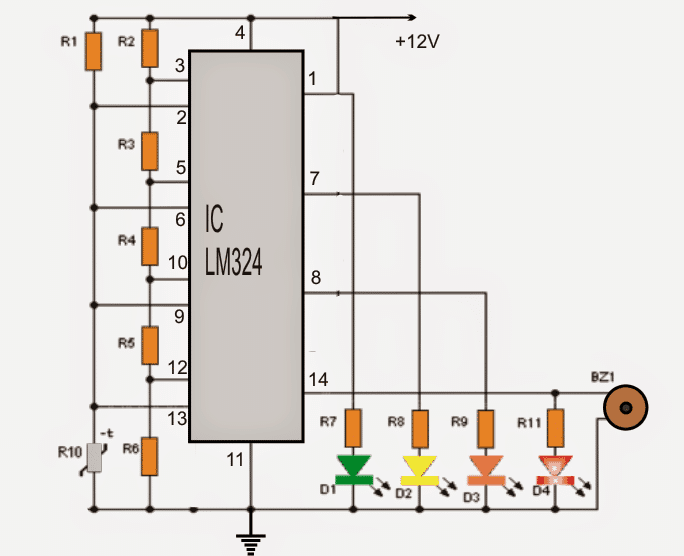

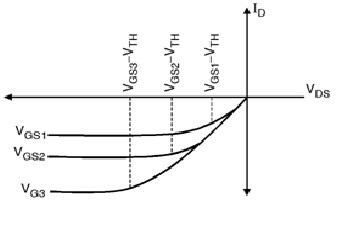

Características del transistor PMOS

Las características del transistor PMOS I-V se muestran a continuación. Estas características se dividen en dos regiones para obtener la relación entre la corriente de drenaje a fuente (I DS), así como sus voltajes terminales como regiones lineales y de saturación.

En una región de revestimiento, el IDS aumentará linealmente cuando aumente el VDS (voltaje de drenaje a fuente), mientras que en la región de saturación, el IDS es estable y es independiente del VDS. La relación principal entre el ISD (corriente de fuente a drenaje) y sus voltajes terminales se deriva de un procedimiento similar del transistor NMOS. En este caso, el único cambio será que los portadores de carga presentes dentro de la capa de inversión son simplemente agujeros. Cuando los agujeros se mueven de la fuente al drenaje, el flujo de corriente también es el mismo.

Así, el signo negativo aparece dentro de la ecuación actual. Además, todas las polarizaciones aplicadas en los terminales del dispositivo son negativas. Entonces, las características ID - VDS del transistor PMOS se muestran a continuación.

La ecuación de corriente de drenaje para el transistor PMOS en la región lineal se da como:

ID = – mp Cox

Del mismo modo, la ecuación de corriente de drenaje para el transistor PMOS en la región de saturación se da como:

ID = – mp Cox (VSG – | VTH |p )^2

Donde 'mp' es la movilidad del hueco & '|VTH| p' es el voltaje de umbral del transistor PMOS.

En la ecuación anterior, el signo negativo indicará que el ID( corriente de drenaje ) fluye desde el drenaje (D) a la fuente (S) mientras que los agujeros fluyen en la dirección opuesta. Cuando la movilidad del agujero es baja en comparación con la movilidad de los electrones, los transistores PMOS sufren la capacidad de la unidad de baja corriente.

Por lo tanto, se trata de una descripción general del transistor PMOS o transistor mos tipo p: fabricación, circuito y su funcionamiento. SGP Los transistores están diseñados con una fuente p, un sustrato n y drenaje. Los portadores de carga de PMOS son agujeros. Este transistor conduce una vez que se aplica un voltaje bajo en la terminal de puerta. Los dispositivos basados en PMOS son menos propensos a sufrir interferencias en comparación con los dispositivos NMOS. Estos transistores se pueden usar como resistencias controladas por voltaje, cargas activas, espejos de corriente, amplificadores de transimpedancia y también se pueden usar en interruptores y amplificadores de voltaje. Aquí hay una pregunta para usted, ¿qué es un transistor NMOS?