En esta publicación, discutimos las calificaciones de avalancha de MOSFET y aprendemos cómo comprender esta calificación en la hoja de datos correctamente, cómo el fabricante prueba el parámetro y las medidas para proteger los MOSFET de este fenómeno.

El parámetro de avalancha no solo ayuda a verificar la robustez de los dispositivos, sino que también ayuda a filtrar los MOSFET más débiles o los que son más susceptibles o están en riesgo de avería.

¿Qué es MOSFET Avalanche Rating?

La clasificación de avalancha del MOSFET es la energía máxima tolerable (milijulios) que un MOSFET puede soportar, cuando su voltaje de fuente de drenaje excede el límite máximo de voltaje de ruptura (BVDSS).

Este fenómeno ocurre normalmente en circuitos de conmutación MOSFET con carga inductiva a través del terminal de drenaje.

Durante los períodos de encendido de los ciclos de conmutación, el inductor se carga, y durante los períodos de apagado, el inductor libera su energía almacenada en forma de contra EMF a través de la fuente-drenaje del MOSFET.

Este voltaje inverso encuentra su camino a través del diodo del cuerpo del MOSFET, y si su valor excede el límite máximo tolerable del dispositivo, hace que se desarrolle un calor intenso dentro del dispositivo causando daños o un daño permanente al dispositivo.

¿Cuándo se introdujo MOSFET Avalanche?

De hecho, el parámetro Avalanche Energy y UIS (conmutación inductiva sin sujeción) no se incluyó en las hojas de datos del MOSFET antes de la década de 1980.

Y fue entonces cuando evolucionó no solo a una especificación de hoja de datos, sino a un parámetro que muchos consumidores comenzaron a exigir que se probara el FET antes de pasar el dispositivo a producción, especialmente, si el MOSFET está siendo diseñado para implementaciones de suministro de energía o conmutación.

Por lo tanto, fue solo después de la década de 1980 que el parámetro de avalancha comenzó a aparecer en las hojas de datos, y luego los técnicos de promoción comenzaron a comprender que cuanto mayor era la calificación de avalancha, más competitivo parecía ser el dispositivo.

Los ingenieros comenzaron a determinar técnicas para experimentar con el parámetro ajustando algunas de sus variables, que se utilizaron para el proceso de prueba.

En términos generales, cuanto mayor es la energía de la avalancha, más duradero y fuerte se vuelve el MOSFET. Por lo tanto, una clasificación de avalancha más grande representa características MOSFET más fuertes.

La mayoría de las hojas de datos FET normalmente tendrán el parámetro de avalancha incluido en su Tabla de calificaciones máximas absolutas, que se puede encontrar directamente en la página de entrada de la hoja de datos. Especialmente, puede ver los parámetros aquí escritos como Avalanche Current y Avalanche Energy, Eas.

Por lo tanto, en las hojas de datos, MOSFET Avalanche Energy se presenta como la cantidad de energía que el MOSFET es capaz de tolerar mientras se somete a la prueba de avalancha, o cuando se cruza la tensión nominal máxima de ruptura del MOSFET.

Avalanche Current y UIS

Esta clasificación de voltaje de ruptura máxima se determina mediante la prueba de corriente de avalancha, que se logra mediante una prueba de conmutación inductiva sin sujeción o la prueba UIS.

Por lo tanto, cuando los ingenieros discuten sobre la corriente UIS, pueden estar refiriéndose a la corriente de avalancha.

Se realiza una prueba de conmutación inductiva sin sujeción para determinar la corriente y, por lo tanto, la energía de avalancha que podría desencadenar la falla del MOSFET.

Como se mencionó anteriormente, estas magnitudes o clasificaciones dependen enormemente de las especificaciones de prueba, en particular, el valor del inductor aplicado en el momento de la prueba.

Configuración de prueba

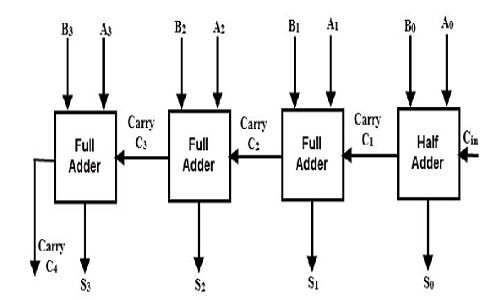

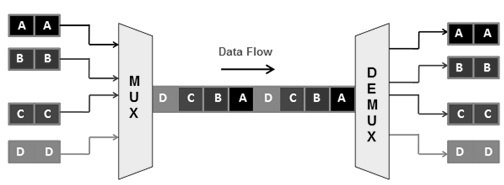

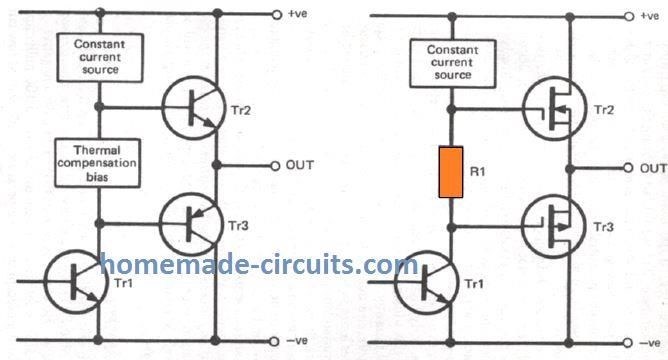

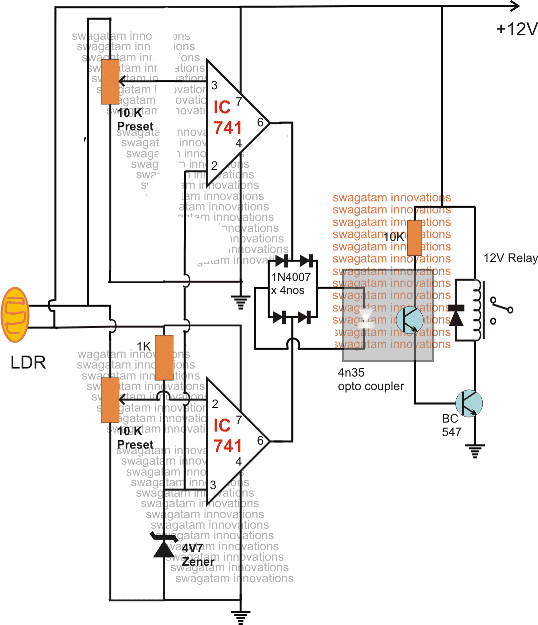

El siguiente diagrama muestra la configuración de un circuito de prueba UIS estándar.

Por lo tanto, vemos un suministro de voltaje en serie con un inductor, L, que también está en serie con el MOSFET bajo prueba. También podemos ver un controlador de puerta para el FET cuya salida está en serie con una resistencia de puerta R de FET.

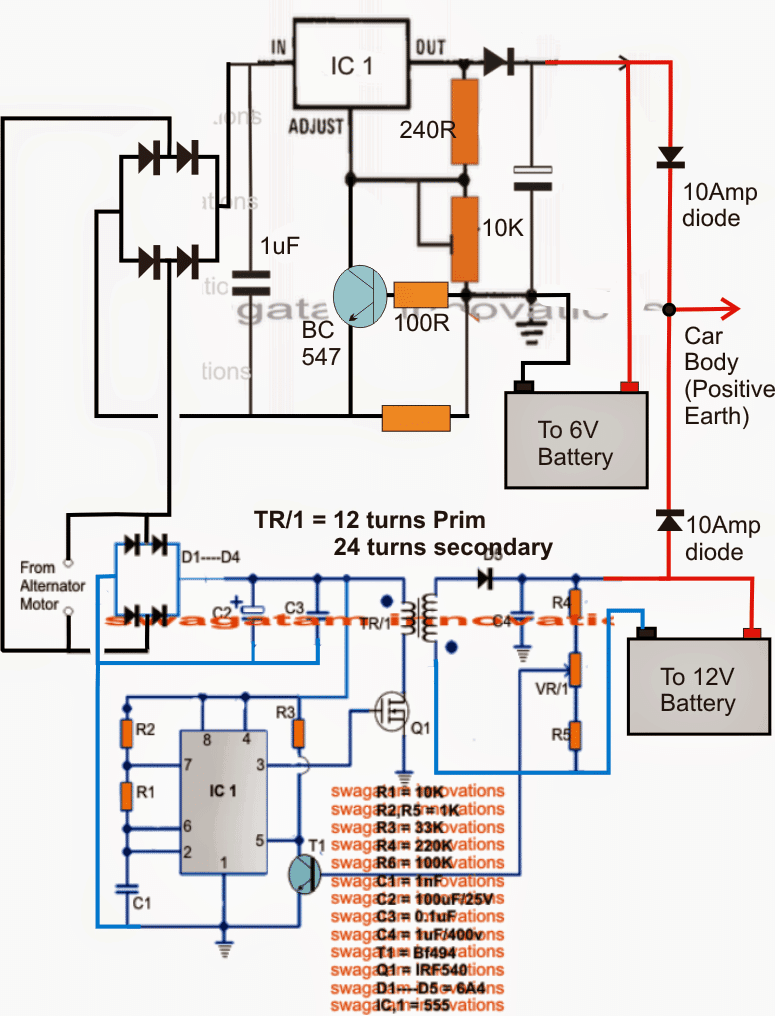

En la imagen de abajo, encontramos el dispositivo controlador LTC55140, que se utiliza en el laboratorio de instrumentos de Texas para evaluar las características UIS del FET.

Posteriormente, la característica UIS ayuda no solo a averiguar la calificación de la hoja de datos FET, sino también el valor utilizado para escanear el FET en el procedimiento de prueba final.

La herramienta permite ajustar el valor del inductor de carga de 0,2 a 160 milhenries. Permite el ajuste del voltaje de drenaje del MOSFET bajo prueba de 10 a 150 voltios.

Esto, como resultado, hace posible filtrar incluso aquellos FET que están clasificados para manejar solo voltaje de ruptura de 100 voltios. Y es posible aplicar corrientes de drenaje de 0,1 a 200 amperios. Y este es el rango de corriente UIS que el FET puede tener que tolerar durante el procedimiento de prueba.

Además, la herramienta permite configurar diferentes rangos de temperaturas de la carcasa del MOSFET, desde -55 a +150 grados.

Procedimientos de prueba

La prueba estándar de UIS se implementa en 4 etapas, como se ilustra en la siguiente imagen:

La primera etapa consiste en la prueba previa a la fuga, en la que el voltaje de suministro polariza el drenaje FET. Básicamente, la idea aquí es tratar de garantizar que el FET funcione de la manera normal esperada.

Por lo tanto, en la primera etapa, el FET se mantiene apagado. Mantiene el voltaje de suministro bloqueado a través de los terminales del emisor daim, sin experimentar ningún tipo de corriente de fuga excesiva que fluya a través de él.

En la segunda etapa, que se conoce como aumento de la corriente de avalancha, el FET se enciende, lo que hace que su voltaje de drenaje disminuya. Esto da como resultado que la corriente aumente gradualmente a través del inductor con una di / dt constante. Entonces, básicamente en esta etapa, se permite que el inductor se cargue.

En la tercera etapa, se realiza la prueba de avalancha propiamente dicha, donde el FET está prácticamente sometido a la avalancha. En esta etapa, el FET se apaga eliminando su polarización de puerta. Esto da como resultado un di / dt masivo que atraviesa el inductor, lo que hace que el voltaje de drenaje del FET se dispare por encima del límite de voltaje de ruptura del FET.

Esto obliga al FET a atravesar la oleada de avalanchas. En este proceso, el FET absorbe toda la energía generada por el inductor y permanece apagado, hasta que se ejecuta la cuarta etapa, que involucra la prueba de post fuga.

En esta cuarta etapa, el FET se somete una vez más a una prueba de avalancha repetida, solo para estar seguro de si el MOSFET todavía se comporta normalmente o no. Si lo hace, se considera que el FET ha pasado la prueba de avalancha.

A continuación, el FET tiene que pasar por la prueba anterior muchas más veces, en donde el nivel de voltaje UIS aumenta gradualmente con cada prueba, hasta el nivel en el que el MOSFET no puede resistir y falla la prueba posterior a la fuga. Y se observa que este nivel de corriente es la capacidad máxima de resistencia a la corriente UIS del MOSFET.

Cálculo de la energía de avalancha de MOSFET

Una vez que se alcanza la capacidad máxima de manejo de corriente UIS del MOSFET, en la cual el dispositivo se descompone, los ingenieros pueden estimar mucho más fácilmente la cantidad de energía que se disipa a través del FET durante el proceso de avalancha.

Suponiendo que toda la energía almacenada en el inductor se disipó en el MOSFET durante la avalancha, esta magnitud de energía se puede determinar utilizando la siguiente fórmula:

ESCOMO= 1 / 2L x IDE2

ESCOMOnos da la magnitud de la energía almacenada dentro del inductor, que es igual al 50% del valor de inductancia multiplicado por la corriente al cuadrado, que fluye a través del inductor.

Más adelante, se observó que a medida que aumentaba el valor del inductor, la cantidad de corriente responsable de la ruptura del MOSFET en realidad disminuía.

Sin embargo, este aumento en el tamaño del inductor compensa de hecho esta reducción en la corriente en la fórmula de energía anterior de una manera que el valor de energía aumenta literalmente.

¿Energía de avalancha o corriente de avalancha?

Estos son los dos parámetros, que pueden confundir a los consumidores, mientras verifican una hoja de datos MOSFET para la clasificación de avalanchas.

Copyright © Texas Instruments Incorporated

Muchos de los fabricantes de MOSFET prueban intencionalmente el MOSFET con inductores más grandes, de modo que puedan presumir de una magnitud de energía de avalancha mayor, creando la impresión de que el MOSFET está probado para resistir grandes energías de avalancha y, por lo tanto, tiene una mayor durabilidad ante avalanchas.

Pero el método anterior de usar un inductor más grande parece engañoso, es exactamente por eso que los ingenieros de Texas Instruments prueban con una inductancia más pequeña del orden de 0.1 mH, por lo que el MOSFET bajo prueba está sujeto a una corriente de avalancha más alta y niveles extremos de tensión de ruptura.

Entonces, en las hojas de datos, no es la energía de la avalancha, sino la corriente de la avalancha la que debería ser mayor en cantidad, lo que muestra una mejor resistencia del MOSFET.

Esto hace que las pruebas finales sean muy estrictas y permite filtrar tantos MOSFET más débiles como sea posible.

Este valor de prueba no solo se usa como el valor final antes de que se pase el diseño FET para la producción, sino que también es el valor que se ingresa en la hoja de datos.

En el siguiente paso, el valor de prueba anterior se reduce en un 65%, de modo que el usuario final pueda obtener un margen más amplio de tolerancia para sus MOSFET.

Entonces, por ejemplo, si la corriente de avalancha probada fue de 125 amperios, el valor final que se ingresa en la hoja de datos resulta ser 81 amperios, después de la reducción.

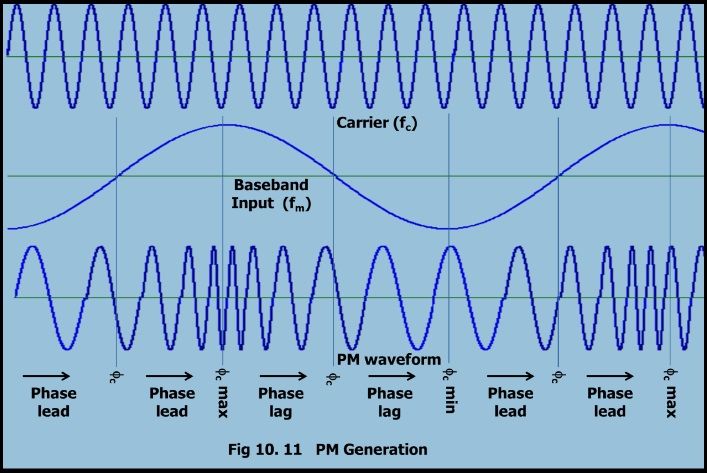

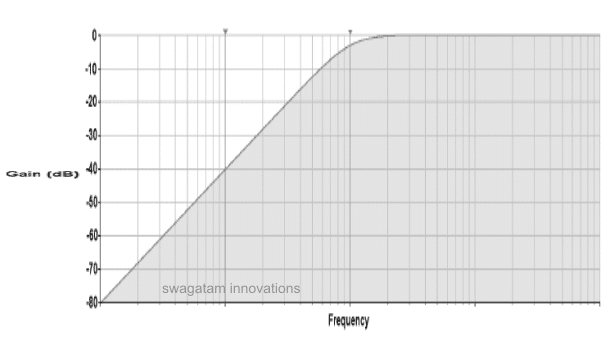

MOSFET Avalanche Current vs Time Pasado en Avalanche

Otro parámetro que está asociado con el MOSFET de potencia y mencionado en las hojas de datos, especialmente para los MOSFET diseñados para aplicaciones de conmutación es la capacidad de corriente de avalancha frente al tiempo empleado en avalancha. Este parámetro se muestra normalmente con respecto a la temperatura de la carcasa del MOSFET a 25 grados. Durante la prueba, la temperatura de la carcasa aumenta a 125 grados.

En esta situación, la temperatura de la caja del MOSFET del MOSFET se acerca mucho a la temperatura de unión real de la matriz de silicio del MOSFET.

En este procedimiento, a medida que aumenta la temperatura de unión del dispositivo, ¿puede esperar ver una cierta degradación, lo cual es bastante normal? Sin embargo, si el resultado muestra un alto nivel de degradación, eso puede indicar los signos de un dispositivo MOSFET inherentemente débil.

Por lo tanto, desde el punto de vista del diseño, se intenta garantizar que la degradación no supere el 30% para un aumento de la temperatura de la carcasa de 25 a 125 grados.

Cómo proteger el MOSFET de la corriente de avalancha

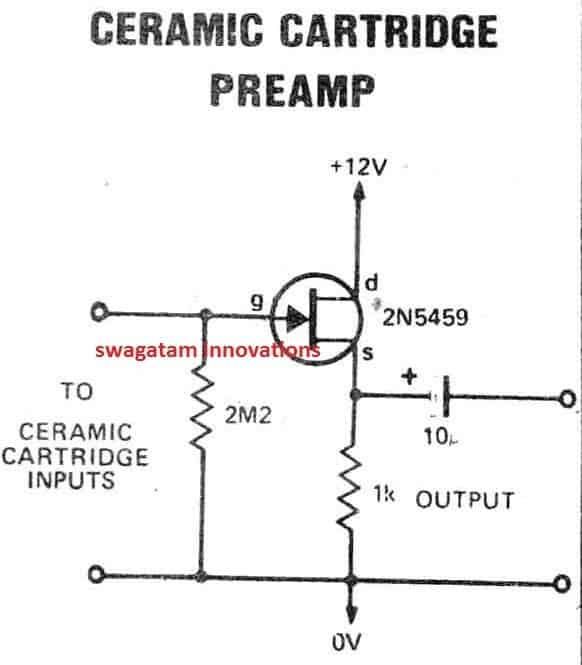

Como aprendimos de las discusiones anteriores, la avalancha en los MOSFET se desarrolla debido a la conmutación inductiva de EMF de alto voltaje a través del diodo del cuerpo del MOSFET.

Si este voltaje EMF trasero excede la clasificación máxima del diodo del cuerpo, causa una generación extrema de calor en el dispositivo y daños posteriores.

Esto implica que si se permite que el voltaje EMF inductivo pase a través de un diodo de derivación externo adecuadamente clasificado, a través del emisor de drenaje del FET puede ayudar a evitar el fenómeno de avalancha.

El siguiente diagrama sugiere el diseño estándar de agregar un diodo emisor de drenaje externo para reforzar el diodo del cuerpo interno del MOSFET.

Cortesía: Avalancha MOSFET

Anterior: Conversión de encendido por chispa desperdiciada en chispa secuencial, para una combustión de alta eficiencia Siguiente: Circuito UPS en línea simple