El término CMOS significa 'Semiconductor de óxido de metal complementario'. Esta es una de las tecnologías más populares en la industria del diseño de chips de computadora y se usa ampliamente hoy en día para formar circuitos integrados en numerosas y variadas aplicaciones. Las memorias de las computadoras, las CPU y los teléfonos móviles actuales utilizan esta tecnología debido a varias ventajas clave. Esta tecnología hace uso de dispositivos semiconductores de canal P y canal N. Una de las tecnologías MOSFET más populares disponibles en la actualidad es la tecnología complementaria MOS o CMOS. Esta es la tecnología de semiconductores dominante para microprocesadores, chips de microcontroladores, memorias como RAM, ROM, EEPROM y Circuitos integrados de aplicaciones específicas (ASIC).

Introducción a la tecnología MOS

En el diseño de circuitos integrados, el componente básico y más esencial es el transistor. Entonces, MOSFET es un tipo de transistor utilizado en muchas aplicaciones. La formación de este transistor se puede hacer como un sándwich al incluir una capa semiconductora, generalmente una oblea, una rebanada de un solo cristal de silicio, una capa de dióxido de silicio y una capa de metal. Estas capas permiten que los transistores se formen dentro del material semiconductor. Un buen aislante como Sio2 tiene una capa delgada con un espesor de cien moléculas.

Los transistores que usamos silicio policristalino (poli) en lugar de metal para sus secciones de puerta. La puerta de polisilicio de FET se puede reemplazar casi utilizando puertas metálicas en circuitos integrados de gran escala. A veces, tanto los FET de polisilicio como los metálicos se denominan IGFET, que significa FET de puerta aislada, porque el Sio2 debajo de la puerta es un aislante.

CMOS (semiconductor complementario de óxido metálico)

El principal ventaja de CMOS sobre NMOS y la tecnología BIPOLAR es la disipación de energía mucho menor. A diferencia de los circuitos NMOS o BIPOLAR, un circuito MOS complementario casi no tiene disipación de potencia estática. La energía solo se disipa en caso de que el circuito realmente cambie. Esto permite integrar más puertas CMOS en un IC que en NMOS o tecnología bipolar , lo que resulta en un rendimiento mucho mejor. El transistor semiconductor de óxido de metal complementario consta de MOS de canal P (PMOS) y MOS de canal N (NMOS). Consulte el enlace para obtener más información sobre el proceso de fabricación del transistor CMOS .

CMOS (semiconductor complementario de óxido metálico)

NMOS

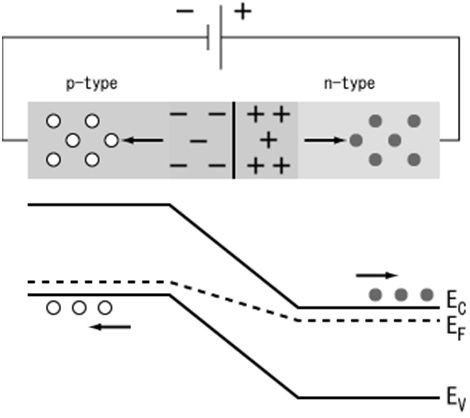

NMOS está construido sobre un sustrato de tipo p con una fuente de tipo ny un drenaje difundido sobre él. En NMOS, la mayoría de los portadores son electrones. Cuando se aplica un alto voltaje a la puerta, el NMOS conducirá. De manera similar, cuando se aplica un voltaje bajo a la puerta, NMOS no conducirá. Se considera que NMOS es más rápido que PMOS, ya que los portadores en NMOS, que son electrones, viajan dos veces más rápido que los agujeros.

Transistor NMOS

PMOS

El MOSFET de canal P consta de una fuente y un drenaje de tipo P difundidos sobre un sustrato de tipo N. La mayoría de los portadores son huecos. Cuando se aplica un alto voltaje a la puerta, el PMOS no conducirá. Cuando se aplica un voltaje bajo a la puerta, el PMOS conducirá. Los dispositivos PMOS son más inmunes al ruido que los dispositivos NMOS.

Transistor PMOS

Principio de funcionamiento CMOS

En la tecnología CMOS, tanto los transistores de tipo N como los de tipo P se utilizan para diseñar funciones lógicas. La misma señal que enciende un transistor de un tipo se usa para apagar un transistor del otro tipo. Esta característica permite el diseño de dispositivos lógicos utilizando solo interruptores simples, sin la necesidad de una resistencia pull-up.

En CMOS puertas lógicas Se dispone una colección de MOSFET de tipo n en una red desplegable entre la salida y el riel de suministro de energía de bajo voltaje (Vss o, con bastante frecuencia, tierra). En lugar de la resistencia de carga de las puertas lógicas NMOS, las puertas lógicas CMOS tienen una colección de MOSFET de tipo p en una red pull-up entre la salida y el riel de mayor voltaje (a menudo llamado Vdd).

CMOS usando Pull Up & Pull Down

Por lo tanto, si tanto un transistor tipo p como un transistor tipo n tienen sus puertas conectadas a la misma entrada, el MOSFET tipo p estará ENCENDIDO cuando el MOSFET tipo n esté APAGADO, y viceversa. Las redes están organizadas de manera que una esté encendida y la otra apagada para cualquier patrón de entrada, como se muestra en la figura siguiente.

CMOS ofrece una velocidad relativamente alta, baja disipación de energía, altos márgenes de ruido en ambos estados y funcionará en una amplia gama de voltajes de fuente y entrada (siempre que el voltaje de la fuente sea fijo). Además, para comprender mejor el principio de funcionamiento del semiconductor de óxido de metal complementario, debemos analizar brevemente las puertas lógicas CMOS como se explica a continuación.

¿Qué dispositivos usan CMOS?

La tecnología como CMOS se utiliza en diferentes chips como microcontroladores, microprocesadores, SRAM (RAM estática) y otros circuitos lógicos digitales. Esta tecnología se utiliza en una amplia gama de circuitos analógicos que incluyen convertidores de datos, sensores de imagen y transceptores altamente incorporados para varios tipos de comunicación.

Inversor CMOS

El circuito inversor como se muestra en la figura siguiente. Consiste en PMOS y NMOS FET . La entrada A sirve como voltaje de puerta para ambos transistores.

El transistor NMOS tiene entrada desde Vss (tierra) y el transistor PMOS tiene entrada desde Vdd. Se emite el terminal Y. Cuando se da un voltaje alto (~ Vdd) en el terminal de entrada (A) del inversor, el PMOS se convierte en un circuito abierto y el NMOS se apaga para que la salida se reduzca a Vss.

Inversor CMOS

Cuando un voltaje de bajo nivel ( La siguiente figura muestra una puerta NAND MOS complementaria de 2 entradas. Consta de dos transistores NMOS en serie entre Y y Tierra y dos transistores PMOS paralelos entre Y y VDD. Si la entrada A o B es 0 lógico, al menos uno de los transistores NMOS estará APAGADO, interrumpiendo la ruta de Y a Tierra. Pero al menos uno de los transistores pMOS estará ENCENDIDO, creando una ruta de Y a VDD. Puerta NAND de dos entradas Por tanto, la salida Y será alta. Si ambas entradas son altas, ambos transistores nMOS estarán ENCENDIDOS y ambos transistores pMOS estarán APAGADOS. Por lo tanto, la salida será lógica baja. La tabla de verdad de la puerta lógica NAND dada en la siguiente tabla. En la figura siguiente se muestra una puerta NOR de 2 entradas. Los transistores NMOS están en paralelo para bajar la salida cuando cualquiera de las entradas es alta. Los transistores PMOS están en serie para elevar la salida cuando ambas entradas son bajas, como se indica en la siguiente tabla. La salida nunca se deja flotando. Puerta NOR de dos entradas La tabla de verdad de la puerta lógica NOR dada en la siguiente tabla. La fabricación de transistores CMOS se puede realizar en la oblea de silicio. El diámetro de la oblea varía de 20 mm a 300 mm. En esto, el proceso de litografía es el mismo que el de la imprenta. En cada paso, se pueden depositar diferentes materiales, grabar o modelar. Este proceso es muy sencillo de entender al ver la parte superior de la oblea y la sección transversal dentro de un método de ensamblaje simplificado. La fabricación de CMOS se puede lograr mediante el uso de tres tecnologías, a saber, N-well pt P-well, Twin well y SOI (Silicon on Insulator). Consulte este enlace para obtener más información sobre Fabricación CMOS . La vida útil típica de una batería CMOS es de aproximadamente 10 años. Pero, esto puede cambiar según la utilización y el entorno donde se encuentre la PC. Cuando falla la batería CMOS, la computadora no puede mantener la fecha y hora exactas en la computadora una vez que está apagada. Por ejemplo, una vez que la computadora está encendida, es posible que vea la hora y la fecha como 12:00 PM y 1 de enero de 1990. Esta falla especifica que la batería del CMOS está fallada. Las características más importantes de CMOS son una baja utilización de energía estática y una gran inmunidad al ruido. Cuando el transistor único del par de transistores MOSFET se apaga, la combinación en serie usa una potencia significativa durante la conmutación entre los dos indicados como ENCENDIDO y APAGADO. Como resultado, estos dispositivos no generan calor residual en comparación con otros tipos de circuitos lógicos como la lógica TTL o NMOS, que por lo general usan algo de corriente permanente incluso sin cambiar su estado. Estas características CMOS permitirán integrar funciones lógicas con alta densidad en un circuito integrado. Debido a esto, CMOS se ha convertido en la tecnología más utilizada para ejecutarse dentro de los chips VLSI. La frase MOS es una referencia a la estructura física del MOSFET que incluye un electrodo con una puerta de metal que se encuentra en la parte superior de un aislante de óxido de material semiconductor. Un material como el aluminio se usa solo una vez, sin embargo, ahora el material es polisilicio. El diseño de otras puertas metálicas se puede realizar mediante un retorno a través de la llegada de materiales dieléctricos de alto κ dentro del proceso del proceso CMOS. Los sensores de imagen como el dispositivo de carga acoplada (CCD) y el semiconductor de óxido metálico complementario (CMOS) son dos tipos diferentes de tecnologías. Estos se utilizan para capturar la imagen digitalmente. Cada sensor de imagen tiene sus ventajas, desventajas y aplicaciones. La principal diferencia entre CCD y CMOS es la forma de capturar el marco. Un dispositivo de carga acoplada como CCD usa un obturador global mientras que el CMOS usa un obturador enrollable. Estos dos sensores de imagen cambian la carga de luz a eléctrica y la procesan en señales electrónicas. El proceso de fabricación utilizado en los CCD es especial para formar la capacidad de mover la carga a través del IC sin alteración. Por lo tanto, este proceso de fabricación puede conducir a sensores de muy alta calidad sobre sensibilidad y fidelidad a la luz. Por el contrario, los chips CMOS utilizan procedimientos de fabricación fijos para diseñar el chip y también se puede utilizar un proceso similar para fabricar los microprocesadores. Debido a las diferencias en la fabricación, hay algunas diferencias claras entre los sensores como CCD 7 CMOS. Los sensores CCD capturarán las imágenes con menos ruido y una gran calidad, mientras que los sensores CMOS suelen ser más propensos al ruido. Por lo general, CMOS usa menos energía mientras que el CCD usa mucha energía como más de 100 veces para el sensor CMOS. La fabricación de chips CMOS se puede realizar en cualquier línea de producción de Si típica porque tienden a ser muy baratos en comparación con los CCD. Los sensores CCD son más maduros porque se producen en masa durante un período prolongado. Tanto los generadores de imágenes CMOS como CCD dependen del efecto fotoeléctrico para generar la señal eléctrica de la luz. Con base en las diferencias anteriores, los CCD se utilizan en cámaras para enfocar imágenes de alta calidad a través de muchos píxeles y una sensibilidad a la luz excepcional. Por lo general, los sensores CMOS tienen menos resolución, calidad y sensibilidad. Un enclavamiento se puede definir como cuando se produce un cortocircuito entre los dos terminales, como la alimentación y la tierra, de modo que se puede generar una corriente alta y se puede dañar el CI. En CMOS, el enganche es la aparición de un rastro de baja impedancia entre el riel de potencia y el riel de tierra debido a la comunicación entre los dos transistores como los parásitos PNP y NPN. transistores . En el circuito CMOS, los dos transistores como PNP y NPN están conectados a dos rieles de suministro como VDD y GND. La protección de estos transistores se puede realizar mediante resistencias. En una transmisión con enclavamiento, la corriente fluirá desde VDD a GND directamente a través de los dos transistores para que pueda ocurrir un cortocircuito, por lo que la corriente extrema fluirá desde VDD a la terminal de tierra. Existen diferentes métodos para prevenir el enganche En la prevención de enganche, se puede colocar una alta resistencia en el camino para detener el flujo de corriente a través del suministro y hacer que β1 * β2 sea inferior a 1 utilizando los siguientes métodos. La estructura del SCR parasitario se marcará en el entorno de transistores como PMOS y NMOS a través de una capa de óxido aislante. La tecnología para la protección de enganche apagará el dispositivo una vez que se note el enganche. Los servicios de prueba de latch-up pueden ser realizados por muchos proveedores en el mercado. Esta prueba se puede realizar mediante una secuencia de intentos para activar la estructura de SCR en el CMOS IC, mientras que los pines relacionados se verifican cuando la sobrecorriente fluye a través de él. Se recomienda obtener las primeras muestras del lote experimental y enviarlas a un laboratorio de pruebas de Latch-up. Esta práctica de laboratorio aplicará la fuente de alimentación máxima posible y luego proporcionará la fuente de corriente a las entradas y salidas del chip cada vez que se produzca un enganche mediante el control del suministro de corriente. Las ventajas de CMOS incluyen las siguientes. Los principales beneficios de CMOS sobre TTL son un buen margen de ruido y un menor consumo de energía. Esto se debe a que no hay un carril de conducción directa desde VDD a GND, los tiempos de caída se basan en las condiciones de entrada, luego la transmisión de la señal digital será fácil y de bajo costo a través de chips CMOS. CMOS se utiliza para explicar la cantidad de memoria en la placa base de la computadora que se almacenará en la configuración del BIOS. Estas configuraciones incluyen principalmente la fecha, la hora y la configuración del hardware Las salidas si CMOS se conducen activamente en ambos sentidos Las desventajas de CMOS incluyen las siguientes. Los procesos MOS complementarios se implementaron ampliamente y han reemplazado fundamentalmente los procesos NMOS y bipolares para casi todas las aplicaciones de lógica digital. La tecnología CMOS se ha utilizado para los siguientes diseños de circuitos integrados digitales. Por lo tanto, la El transistor CMOS es muy famoso porque utilizan la energía eléctrica de manera eficiente. No usan suministro eléctrico cuando cambian de una condición a otra. Además, los semiconductores complementarios funcionan mutuamente para detener el voltaje de o / p. El resultado es un diseño de baja potencia que proporciona menos calor, debido a esta razón, estos transistores han cambiado otros diseños anteriores como los CCD dentro de los sensores de la cámara y se utilizan en la mayoría de los procesadores actuales. La memoria del CMOS dentro de una computadora es una especie de RAM no volátil que almacena la configuración del BIOS y la información de fecha y hora. Creo que ha comprendido mejor este concepto. Además, cualquier consulta sobre este concepto o proyectos de electrónica , dé sus valiosas sugerencias comentando en la sección de comentarios a continuación. Aquí hay una pregunta para usted, ¿por qué CMOS es preferible a NMOS? APORTE ENTRADA LÓGICA PRODUCCIÓN SALIDA LÓGICA 0 v 0 Vdd 1 Vdd 1 0 v 0 Puerta CMOS NAND

A B Red desplegable Pull-up Network SALIDA Y 0 0 APAGADO EN 1 0 1 APAGADO EN 1 1 0 APAGADO EN 1 1 1 EN APAGADO 0 Puerta NOR CMOS

A B Y 0 0 1 0 1 0 1 0 0 1 1 0 Fabricación CMOS

Una vida útil de la batería CMOS

Síntomas de falla de la batería CMOS

Características CMOS

CCD frente a CMOS

En algunas aplicaciones, los sensores CMOS están mejorando recientemente hasta el punto en que alcanzan una igualdad cercana con los dispositivos CCD. Generalmente, las cámaras CMOS no son caras y tienen una gran duración de la batería.Latch-Up en CMOS

Ventajas

TTL es un circuito lógico digital donde los transistores bipolares funcionan con pulsos de CC. Varias puertas lógicas de transistores normalmente están formadas por un solo CI.Desventajas

Aplicaciones CMOS