Generalmente, el restador completo es uno de los más utilizados y circuitos lógicos combinacionales esenciales . Es un dispositivo electrónico básico, que se utiliza para realizar la resta de dos números binarios. En el artículo anterior, ya hemos dado la teoría básica de medio sumador y un sumador completo que utiliza los dígitos binarios para el cálculo. Asimismo, el restador completo usa dígitos binarios como 0,1 para la resta. El circuito de este se puede construir con puertas lógicas como OR, Ex-OR, puerta NAND. Las entradas de este restador son A, B, Bin y las salidas son D, Bout.

Este artículo da una idea de la teoría del restador completo que comprende premisas como qué es un sustractor, diseño con puertas lógicas, tabla de verdad, etc. Este artículo es útil para estudiantes de ingeniería que pueden analizar estos temas en el laboratorio práctico de HDL.

¿Qué es un sustractor?

La resta de dígitos binarios se puede hacer con la ayuda del circuito de resta. Este es un tipo de circuito lógico combinacional, que se utiliza para realizar la resta de dos dígitos binarios como 0 y 1. La resta de dígitos binarios de 0 a 0 o de 0 a 1 no altera el resultado, la resta de 1 a 1 dará como resultado 0, pero la resta de 1 a 0 necesita un préstamo.

Por ejemplo, el circuito de resta de dos bits incluye dos entradas como A y B, mientras que las salidas son diferencia y prestadas. Este circuito se puede construir con sumadores junto con inversores que se encuentran entre cada entrada de datos, así como la entrada prestada (Bin) de la fase anterior de FA.

Los restadores se clasifican en dos tipos como medio restador y resta completo. Aquí estamos discutiendo el restador completo.

¿Qué es un restador completo?

Es un dispositivo electrónico o circuito lógico que realiza la resta de dos dígitos binarios. Es un circuito lógico combinacional utilizado en electrónica digital. Muchos circuitos combinacionales están disponibles en tecnología de circuito integrado a saber, sumadores, codificadores, decodificadores y multiplexores. En este artículo, vamos a discutir su construcción usando medio resta y también los términos como tabla de verdad.

Sustractor completo

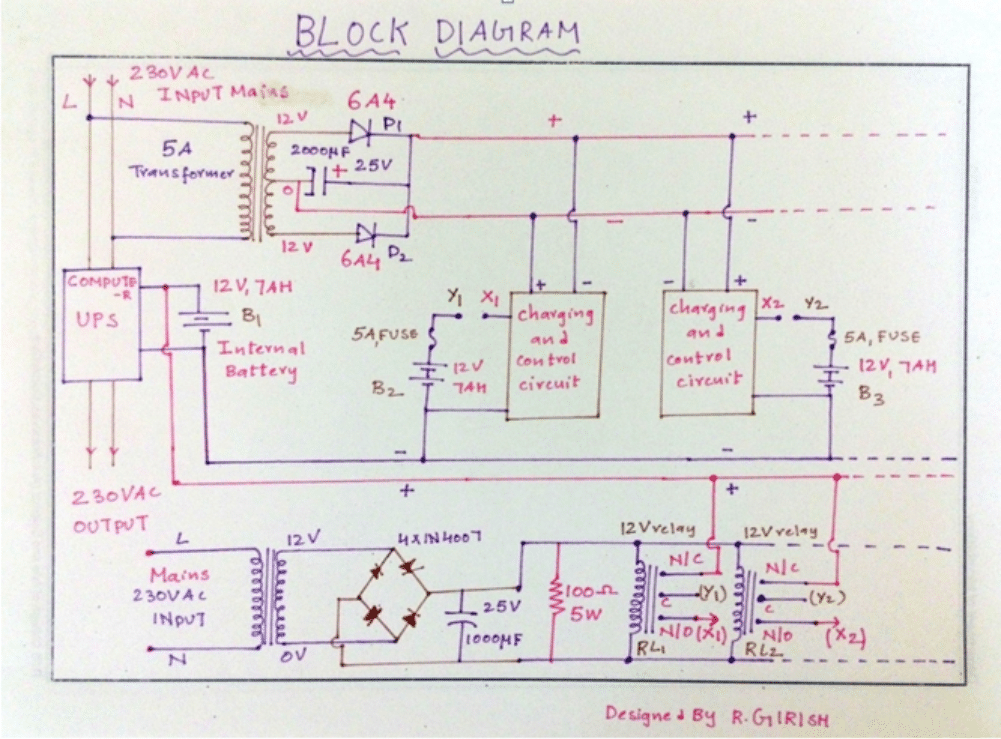

El diseño de esto se puede hacer mediante dos medios restadores, lo que implica tres entradas como minuendo, resta y préstamo, el bit prestado entre las entradas se obtiene de la resta de dos dígitos binarios y se resta del siguiente par de orden superior de bits, salidas como diferencia y pedir prestado.

los diagrama de bloques de resta completo se muestra a continuación. La principal desventaja del medio restador es que no podemos hacer un bit prestado en este resta. Mientras que en su diseño, en realidad podemos hacer un bit prestado en el circuito y podemos restar con los dos i / ps restantes. Aquí A es el minuendo, B es el sustraendo y Bin se toma prestado. Las salidas son Diferencia (Diff) y Bout (Pedir prestado). El circuito de resta completo se puede obtener usando dos medios sustractores con una puerta OR adicional.

Diagrama de circuito de restador completo con puertas lógicas

los Diagrama de circuito del restador completo usando puerta básica s se muestra en el siguiente diagrama de bloques. Este circuito se puede hacer con dos circuitos de medio substractor.

En el circuito inicial de medio sustractor, las entradas binarias son A y B. Como hemos discutido en el artículo anterior sobre medio sustractor, generará dos salidas, a saber, diferencia (Diff) y Borrow.

Sustractor completo usando puertas lógicas

La diferencia o / p del restador de la izquierda se da al circuito de la mitad del substractor izquierdo. La salida diferencial se proporciona además a la entrada de la mitad derecha del circuito Subtractor. Ofrecimos el Préstamo en bits a través del otro i / p del siguiente medio circuito sustractor . Una vez más, dará tanto Diff como Pedir prestado el bit. La salida final de este sustractor es salida diferencial.

Por otro lado, el Préstamo de los dos circuitos de la mitad del Subtractor está conectado a la puerta lógica OR. Después de dar la lógica OR para dos bits de salida del sustractor, adquirimos el préstamo final del sustractor. El último préstamo para significar el MSB (un bit más significativo).

Si observamos el circuito interno de este, podemos ver dos Half Subtractors con puerta NAND y puerta XOR con una puerta OR extra.

Tabla completa de verdad de sustractores

Esta circuito sustractor ejecuta una resta entre dos bits, que tiene 3 entradas (A, B y Bin) y dos salidas (D y Bout). Aquí las entradas indican minuendo, sustraendo y préstamo anterior, mientras que las dos salidas se indican como préstamo o / py diferencia. La siguiente imagen muestra la tabla de verdad del restador completo.

Entradas | Salidas | |||

Minuendo (A) | Sustraendo (B) | Pedir prestado (Bin) | Diferencia (D) | Pedir prestado (pelea) |

0 | 0 | 0 | 0 | 0 |

0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

1 | 1 | 0 | 0 | 0 |

1 | 1 | 1 | 1 | 1 |

K-Map

La simplificación del mapa K de resta completo para la diferencia anterior y pedir prestado se muestra a continuación.

Las ecuaciones para la diferencia y Bin se mencionan a continuación.

La expresión de Diferencia es,

D = A'B'Bin + AB'Bin '+ A'BBin' + ABBin

La expresión para pedir prestado es,

Combate = A'Bin + A'B + BBin

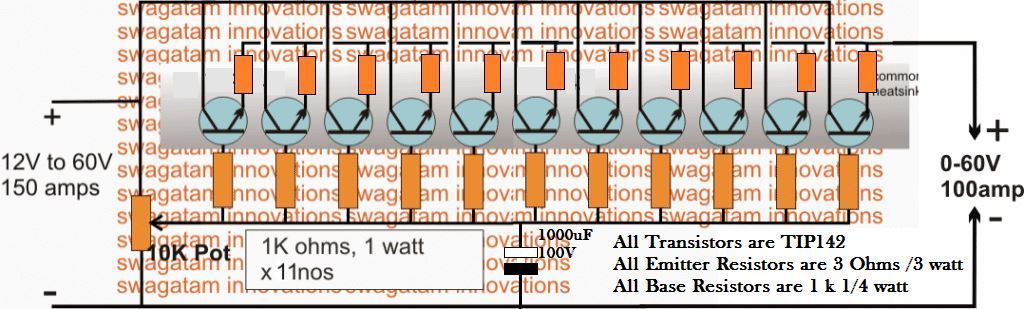

Conexión en cascada del circuito del sustractor completo

Anteriormente, hemos discutido una descripción general de esta construcción similar, diagrama de circuito con puertas lógicas. Pero si queremos restar dos números que de otro modo serían más de 1 bit, este circuito de resta es muy útil para poner en cascada números de un solo bit y también resta más de dos números binarios. En tales casos, se utiliza un circuito en cascada sumador completo con la ayuda de una puerta lógica NOT. La conversión del circuito de sumador completo a restador completo se puede realizar utilizando la técnica del complemento a 2.

En general, invierta las entradas de sustraendos para el sumador completo utilizando NOT gate, de lo contrario, un inversor. Al agregar este Minuendo (entrada no invertida) y Subtraendo (Entrada invertida), el LSB (entrada de acarreo) del circuito FA es 1, lo que significa Lógica alta; de lo contrario, restamos dos dígitos binarios usando la técnica del complemento a 2. La salida del FA es el bit Diff y, si invertimos la ejecución, podemos obtener el bit MSB, de lo contrario, tomar prestado. De hecho, podemos diseñar el circuito de modo que se pueda observar la salida.

Código Verilog

Para la parte de codificación, primero, debemos verificar la forma estructural de modelado del diagrama de circuito lógico. El diagrama lógico de esto se puede construir usando una puerta Y, circuitos de medio restador y la combinación de puertas lógicas como puertas Y, O, NO, XOR. Como en el modelado estructural, explicamos varios módulos para cada arreglo elemental básico. En el siguiente código, se pueden definir diferentes módulos para cada puerta.

Este módulo es para la puerta OR.

ENTRADA: a0, b0

SALIDA: c0

Por último, uniremos estos módulos de puerta precisa en un único módulo. Para eso, aquí utilizamos la instanciación de module. Ahora, esta instanciación se puede usar una vez que queramos replicar un módulo o función exactos para diversos conjuntos de entrada. Primero, diseñamos un medio restador y luego este módulo se usa para implementar un restador completo. Para implementar esto, usamos la puerta OR para combinar el o / ps para la variable de Bout. los código verilog para el restador completo se muestra a continuación

módulo or_gate (a0, b0, c0)

entrada a0, b0

salida c0

asignar c0 = a0 | b0

endmodule

módulo xor_gate (a1, b1, c1)

entrada a1, b1

salida c1

asignar c1 = a1 ^ b1

endmodule

módulo y_puerta (a2, b2, c2)

entrada a2, b2

salida c2

asignar c2 = a2 y b2

endmodule

módulo not_gate (a3, b3)

entrada a3

salida b3

asignar b3 = ~ a3

endmodule

módulo half_subtractor (a4, b4, c4, d4)

entrada a4, b4

salida c4, d4

alambre x

xor_gate u1 (a4, b4, c4)

and_gate u2 (x, b4, d4)

not_gate u3 (a4, x)

endmodule

módulo full_subtractor (A, B, Bin, D, Bout)

entrada A, B, Bin

salida D, Bout

alambre p, q, r

mitad_sustractor u4 (A, B, p, q)

half_subtractor u5 (p, Bin, D, r)

or_gate u6 (q, r, combate)

endmodule

Sustractor completo usando multiplexor 4X1

La ejecución de la resta se puede realizar mediante el método del complemento a dos. Por lo tanto, necesitamos utilizar una puerta 1-XOR que se usa para invertir 1 bit e incluir uno en el bit de acarreo. La salida de DIFFERENCE es similar a la SUMA de salida en el circuito de sumador completo, sin embargo, el o / p de BARROW no es similar a la salida de acarreo del sumador completo, sin embargo, se invierte y se complementa, como A - B = A + (-B) = A + complemento a dos de B.

El diseño de este utilizando multiplexor 4X1 se muestra en el siguiente diagrama lógico. Este diseño se puede realizar siguiendo los siguientes pasos.

Multiplexor 4X1

- En el paso 1, hay dos salidas como Sub y Borrow. Entonces tenemos que elegir 2 multiplexores.

- En el paso 2, la tabla de verdad se puede implementar junto con K-maps

- En el paso 3, las dos variables se pueden seleccionar como su línea de selección. Por ejemplo, B & C son en este caso.

Mesa de la verdad

los tabla de verdad del restador completo El circuito que usa multiplexor 4X1 incluye lo siguiente

A | B | C | Sub | Pedir prestado |

0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

1 | 1 | 1 | 1 | 1 |

Sustractor completo usando decodificador

El diseño de un restador completo usando 3-8 decodificadores se puede hacer usando salidas bajas activas. Supongamos que el decodificador funciona utilizando el siguiente diagrama lógico. El decodificador incluye tres entradas en 3-8 decodificadores. Con base en la tabla de verdad, podemos escribir los términos mínimos para las salidas de diferencia y préstamo.

De la tabla de verdad anterior,

Para las diferentes funciones en la tabla de verdad, los minitérminos se pueden escribir como 1,2,4,7 y, de manera similar, para el préstamo, los minitérminos se pueden escribir como 1,2,3,7. Los decodificadores 3-8 incluyen tres entradas y 8 salidas de 0 a 7 números.

Decodificador de 3 a 8

Si la entrada del restador es 000, entonces la salida '0' estará activa y si la entrada es 001, entonces la salida '1' estará activa.

Ahora las salidas del restador se pueden tomar de 1, 2, 4 y 7 para conectarlo a una puerta NAND, entonces la salida será la diferencia. Estas salidas se pueden conectar a otras puertas lógicas NAND donde la salida cambia al préstamo.

Por ejemplo, si la entrada es 001, entonces la salida será 1, lo que significa que está activa. Entonces, la salida es activa baja y la salida se puede obtener de la puerta NAND llamada función de diferencia como alta y la función de préstamo también cambia a alta. Por lo tanto, obtenemos la salida preferida. Entonces, finalmente, el decodificador funciona como un restador completo.

Ventajas y desventajas

los ventajas del restador Incluya lo siguiente.

- El diseño del restador es muy simple, así como implementar

- Deducción de potencia dentro de DSP (procesamiento de señal digital)

- Las tareas computacionales se pueden realizar a gran velocidad.

los desventajas del restador Incluya lo siguiente.

- En el medio resta, no hay ninguna condición para aceptar una entrada similar a un préstamo de la fase anterior.

- La velocidad del restador puede ser parcial a través del retraso en el circuito.

Aplicaciones

Algunos de los aplicaciones de resta completo Incluya lo siguiente

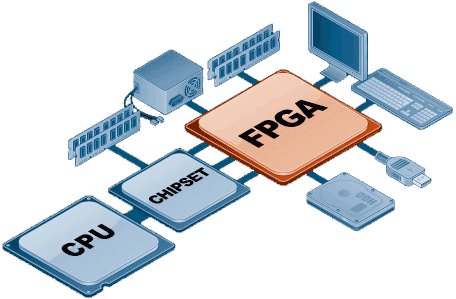

- Estos se emplean generalmente para ALU (unidad lógica aritmética) en computadoras para restar como CPU y GPU para las aplicaciones de gráficos para disminuir la dificultad del circuito.

- Los sustractores se utilizan principalmente para realizar funciones aritméticas como la resta, tanto en calculadoras electrónicas como en dispositivos digitales.

- Estos también son aplicables para diferentes microcontroladores para resta aritmética, temporizadores y contador de programa (PC)

- Los restadores se utilizan en procesadores para calcular tablas, direcciones, etc.

- También es útil para DSP y sistemas basados en redes.

- Estos se utilizan principalmente para ALU dentro de las computadoras para restar como CPU y GPU para aplicaciones gráficas para reducir la complejidad del circuito.

- Estos se utilizan principalmente para realizar funciones aritméticas como la resta dentro de dispositivos digitales, calculadoras, etc.

- Estos sustractores también son apropiados para varios microcontroladores para temporizadores, PC (contador de programa) y resta aritmética

- Estos se emplean para que los procesadores calculen direcciones, tablas, etc.

- La implementación de esto con puertas lógicas como NAND & NOR se puede hacer con cualquier circuito lógico de resta completo porque tanto las puertas NOR como NAND se llaman puertas universales.

A partir de la información anterior, al evaluar el sumador, el restador completo usando dos circuitos de medio resta, y sus formas tabulares, se puede notar que Dout en el restador completo es exactamente similar al Sout del sumador completo. La única variación es que A (variable de entrada) se complementa en el resta completo. Por lo tanto, es posible cambiar el circuito sumador completo en un restador completo simplemente complementando el i / p A antes de que se le dé a las puertas lógicas para generar la última salida de bits prestados (Bout).

Al usar cualquier circuito lógico de sustractor completo, se puede implementar un sustractor completo que usa puertas NAND y un restador completo que usa puertas nor, ya que las puertas NAND y NOR se tratan como puertas universales. Aquí hay una pregunta para ti, ¿cuál es la diferencia entre medio resta y resta completo?