los Transistor de efecto de campo (FET) es un dispositivo electrónico en el que un campo eléctrico se utiliza para regular el flujo de corriente. Para implementar esto, se aplica una diferencia de potencial a través de la puerta y los terminales de la fuente del dispositivo, lo que altera la conductividad entre los terminales de drenaje y de fuente, lo que hace que fluya una corriente controlada a través de estos terminales.

Hechos are called transistores unipolares porque están diseñados para funcionar como dispositivos de tipo portador único. Encontrará diferentes tipos de transistores de efecto de campo disponibles.

Símbolo

Los símbolos gráficos para los JFET de canal ny canal p se pueden visualizar en las siguientes figuras.

Puede notar claramente que las marcas de flecha que apuntan hacia adentro para el dispositivo de canal n indican la dirección en la queGRAMO(corriente de puerta) se supone que fluye cuando la unión p-n tiene polarización directa.

En el caso de un dispositivo de canal p, las condiciones son idénticas excepto la diferencia en la dirección del símbolo de flecha.

Diferencia entre FET y BJT

El transistor de efecto de campo (FET) es un dispositivo de tres terminales diseñado para una amplia gama de aplicaciones de circuitos que complementan, a un gran nivel, las del transistor BJT.

Si bien encontrará variaciones significativas entre BJT y JFET, en realidad hay varias características de coincidencia de las que se hablará en las siguientes discusiones. La principal distinción entre estos dispositivos es que BJT es un dispositivo controlado por corriente como se representa en la Fig. 5.1a, mientras que el transistor JFET es un dispositivo controlado por voltaje como se indica en la Fig. 5.1b.

En pocas palabras, el yo actualCen la figura 5.1a es una función inmediata del nivel de IB. Para el FET la corriente I es función del voltaje VGSdado al circuito de entrada como se muestra en la figura 5.1b.

En ambos casos, la corriente del circuito de salida estará gobernada por un parámetro del circuito de entrada. En una situación un nivel de corriente y en la otra un voltaje aplicado.

Al igual que npn y pnp para transistores bipolares, encontrará transistores de efecto de campo de canal n y canal p. Pero, debe recordar que el transistor BJT es un dispositivo bipolar cuyo prefijo bi- indica que el nivel de conducción es función de dos portadores de carga, electrones y huecos.

El FET por otro lado es un dispositivo unipolar eso depende únicamente de la conducción de electrones (canal n) o de huecos (canal p).

La frase 'efecto de campo' se puede explicar así: todos somos conscientes del poder de un imán permanente para atraer limaduras de metal hacia el imán sin ningún contacto físico. De manera muy similar, dentro del FET se crea un campo eléctrico por las cargas existentes que influyen en la ruta de conducción del circuito de salida sin tener ningún contacto directo entre las cantidades controladas y controladas. Probablemente una de las características más importantes del FET es su alta impedancia de entrada.

Con una magnitud de 1 a varios cientos de megaohmios, supera significativamente los rangos de resistencia de entrada normales de las configuraciones BJT, un atributo extremadamente importante al desarrollar modelos de amplificadores de CA lineales.

Sin embargo, el BJT tiene una mayor sensibilidad a las variaciones en la señal de entrada. Es decir, el cambio en la corriente de salida suele ser significativamente mayor para los BJT que para los FET para la misma cantidad de cambio en sus voltajes de entrada.

Debido a esto, las ganancias de voltaje de CA estándar para los amplificadores BJT pueden ser mucho más altas en comparación con los FET.

En términos generales, los FET son considerablemente más resistentes térmicamente que los BJT, y también suelen tener una estructura de menor tamaño en comparación con los BJT, lo que los hace especialmente adecuados para incrustarse como circuito integrado (IC)papas fritas.

Las características estructurales de algunos FET, por otro lado, pueden permitirles ser más sensibles a los contactos físicos que los BJT.

Más relación BJT / JFET

- Para un BJT VSER= 0,7 V es el factor importante para iniciar un análisis de su configuración.

- Del mismo modo, el parámetro IGRAMO= 0 A es comúnmente lo primero que se considera para el análisis de un circuito JFET.

- Para la configuración BJT,Bes a menudo el primer factor que es necesario determinar.

- Asimismo, para el JFET, es típicamente el VGS.

En este artículo nos centraremos en los JFET o transistores de efecto de campo de unión, en el próximo artículo discutiremos sobre el transistor de efcet de campo semiconductor de óxido metálico o MOS-FET.

CONSTRUCCIÓN Y CARACTERÍSTICAS DE JFET

Como aprendimos anteriormente, un JFET tiene 3 derivaciones. Uno de ellos controla el flujo de corriente entre los otros dos.

Al igual que los BJT, en los JFET también el dispositivo de canal n se usa de manera más prominente que los dispositivos de canal p, ya que los dispositivos n tienden a ser más eficientes y fáciles de usar en comparación con el dispositivo p.

En la siguiente figura podemos ver la estructura o construcción básica de un JFET de canal n. Podemos ver que la composición de tipo n forma el canal principal a través de las capas de tipo p.

La parte superior del canal tipo n está unida a través de un contacto óhmico con un terminal llamado drenaje (D), mientras que la sección inferior del mismo canal también se conecta a través de un contacto óhmico con otro terminal llamado fuente (S).

El par de materiales de tipo p están unidos con el terminal denominado puerta (G). Esencialmente, encontramos que los terminales de drenaje y fuente están unidos a los extremos del canal de tipo n. El terminal de puerta está unido a un par de material de canal p.

Cuando no se aplica voltaje a través de un jfet, sus dos uniones p-n no tienen condiciones de polarización. En esta situación, existe una región de agotamiento en cada unión como se indica en la figura anterior, que se parece bastante a una región p-n de diodo sin polarización.

Analogía del agua

Las operaciones de trabajo y control de un JFET se pueden entender a través de la siguiente analogía con el agua.

Aquí, la presión del agua se puede comparar con la magnitud del voltaje aplicado desde el drenaje hacia la fuente.

El flujo de agua se puede comparar con el flujo de electrones. La boca del grifo imita la terminal de la fuente del JFET, mientras que la parte superior del grifo donde se fuerza el agua muestra el drenaje del JFET.

La perilla de tap actúa como la puerta del JFET. Con la ayuda de un potencial de entrada, controla el flujo de electrones (carga) desde el drenaje a la fuente, al igual que la perilla del grifo controla el flujo de agua en la boca.

De la estructura JFET podemos ver que el drenaje y los terminales de la fuente están en los extremos opuestos del canal n, y como el término se basa en el flujo de electrones, podemos escribir:

VGS= 0 V, VDSAlgún valor positivo

En la Fig 5.4 podemos ver un voltaje positivo VDSaplicado a través del canal n. El terminal de la puerta se une directamente a la fuente para crear una condición VGS= 0V. Esto permite que la puerta y los terminales de la fuente estén en un potencial idéntico, y da como resultado una región de agotamiento del extremo inferior de cada material p, exactamente como vemos en el primer diagrama anterior con una condición sin polarización.

Tan pronto como un voltaje VDD(= VDS), los electrones son empujados hacia el terminal de drenaje, generando el flujo convencional de corriente ID, como se indica en la Fig. 5.4.

La dirección del flujo de la carga revela que el drenaje y la fuente de corriente son iguales en magnitud (ID= YoS). Según las condiciones que se muestran en la Fig. 5.4, el flujo de la carga parece bastante irrestricto y solo se ve afectado por la resistencia del canal n entre el drenaje y la fuente.

Puede observar que la región de agotamiento es más grande alrededor de la sección superior de ambos materiales de tipo p. Esta diferencia de tamaño de la región se explica idealmente a través de la Fig. 5.5. Imaginemos tener una resistencia uniforme en el canal n, esto podría dividirse en las secciones indicadas en la Fig. 5.5.

El actual yoDpuede construir los rangos de voltaje a través del canal como se indica en la misma figura. Como resultado, la región superior del material de tipo p se polarizará inversamente en un nivel de alrededor de 1,5 V, y la región inferior estará simplemente polarizada inversamente en 0,5 V.

El punto en el que la unión p-n tiene polarización inversa a lo largo de todo el canal da lugar a una corriente de puerta con cero amperios, como se muestra en la misma figura. Esta característica que me lleva aGRAMO= 0 A es una característica importante del JFET.

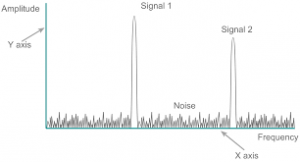

Como VDSel potencial aumenta de 0 a algunos voltios, la corriente aumenta según la ley de Ohm y la gráfica de IDlínea 5DSpuede verse como se demuestra en la Fig. 5.6.

La rectitud comparativa del trazado muestra que para las regiones de valor bajo de VDS, la resistencia es básicamente uniforme. Como VDSsube y se acerca a un nivel conocido como VP en la figura 5.6, las regiones de agotamiento se ensanchan como se muestra en la figura 5.4.

Esto da como resultado una aparente disminución del ancho del canal. La ruta de conducción disminuida conduce al aumento de la resistencia dando lugar a la curva de la figura 5.6.

Cuanto más horizontal se vuelve la curva, mayor es la resistencia, lo que indica que la resistencia se está acercando a ohmios 'infinitos' en la región horizontal. Cuando VDSaumenta hasta un punto en el que parecería que las dos regiones de agotamiento podrían 'entrar en contacto' como se muestra en la Fig. 5.7, da lugar a una situación conocida como pellizco.

La cantidad por la cual VDSdesarrolla esta situación se llama quitar con los dedos voltaje y está simbolizado por VPAGcomo se presenta en la Fig. 5.6. En general, la palabra pellizcar es engañosa porque implica la I actualDse 'pellizca' y cae a 0 A. Como se demuestra en la figura 5.6, esto apenas parece evidente en este caso. IDconserva un nivel de saturación caracterizado como IDSSen la figura 5.6.

La verdad es que sigue existiendo un canal muy pequeño, con una corriente de concentración significativamente alta.

El punto en el que la identificación no cae quitar con los dedos y conserva el nivel de saturación como se indica en la Fig. 5.6 se confirma con la siguiente prueba:

Dado que no hay corriente de drenaje, se elimina la posibilidad de diversos niveles de potencial a través del material del canal n para determinar las cantidades cambiantes de polarización inversa a lo largo de la unión p-n. El resultado final es la pérdida de la distribución de la región de agotamiento que desencadenó quitar con los dedos para empezar.

A medida que aumentamos VDSpor encima de VPAG, la región de contacto cercano donde las dos regiones de agotamiento se encontrarán entre sí aumentará de longitud a lo largo del canal. Sin embargo, el nivel de ID sigue prácticamente sin cambios.

Así, el momento VDSes mayor que Vpag, el JFET adquiere las características de fuente actual.

Como se demuestra en la Fig. 5.8, la corriente en un JFET se determina en ID= YoDSS, pero voltaje VDSmayor que VP es establecido por la carga conectada.

La selección de la notación IDSS se basa en el hecho de que la corriente de drenaje a fuente tiene un enlace en cortocircuito entre la puerta y la fuente.

Una investigación más profunda nos da la siguiente evaluación:

IDSSes la corriente de drenaje más alta para un JFET y se establece mediante las condiciones VGS= 0 V y VDS> | VP |.

Observe que en la figura 5.6 VGSes 0V para el tramo completo de la curva. En las siguientes secciones, aprenderemos cómo los atributos de la figura 5.6 se ven influenciados a medida que el nivel de VGSes variado.

VGS <0V

La volatilidad aplicada a través de la puerta y la fuente se denomina VGS, que es responsable de controlar las operaciones de JFET.

Si tomamos el ejemplo de un BJT, al igual que las curvas de ICvs VESTAse determinan para varios niveles de IB, igualmente las curvas de IDvs VDSpara varios niveles de VGSse puede crear para una contraparte JFET.

Para esto, el terminal de la puerta se establece en un potencial más bajo continuo por debajo del nivel del potencial de la fuente.

Refiriéndose a la figura 5.9 a continuación, se aplica un -1V a través de los terminales de puerta / fuente para un V reducidoDSnivel.

El objetivo del sesgo potencial negativo VGSes desarrollar regiones de agotamiento que se asemejen a la situación de VGS= 0, pero a V significativamente reducidoDS.

Esto hace que la puerta alcance un punto de saturación con niveles más bajos de VDScomo se indica en la Fig. 5.10 (VGS= -1V).

El nivel de saturación correspondiente para IDse puede encontrar que se reduce y en realidad continúa disminuyendo a medida que VGSse hace más negativo.

Puede ver claramente en la figura 5.10 cómo el voltaje de pellizco continúa cayendo con una forma parabólica como VGSse vuelve cada vez más negativo.

Finalmente, cuando VGS= -Vpag, se vuelve lo suficientemente negativo para establecer un nivel de saturación que eventualmente es 0 mA. En este nivel, el JFET está completamente 'APAGADO'.

El nivel de VGSlo que causa que yoDpara llegar a 0 mA se caracteriza por VGS= VPAG, donde VPAGes un voltaje negativo para dispositivos de canal n y un voltaje positivo para JFET de canal p.

Por lo general, puede encontrar la mayoría de las hojas de datos JFET mostrando quitar con los dedos voltaje especificado como VGS (apagado)en lugar de VPAG.

El área en el lado derecho del lugar de pellizco en la figura anterior es el lugar que se usa convencionalmente en los amplificadores lineales para lograr una señal sin distorsión. Esta región generalmente se llama región de amplificación lineal, saturación o de corriente constante.

Resistencia controlada por voltaje

El área que está en el lado izquierdo del lugar geométrico de pellizco en la misma figura, se llama región óhmica o la región de resistencia controlada por voltaje.

En esta región, el dispositivo puede funcionar de hecho como una resistencia variable (por ejemplo, en una aplicación de control automático de ganancia), con su resistencia controlada a través del potencial de puerta / fuente aplicado.

Puede ver que la pendiente de cada una de las curvas que también significa la resistencia de drenaje / fuente del JFET para VDS

A medida que aumentamos VGS con potencial negativo, la pendiente de cada curva se vuelve cada vez más horizontal, exhibiendo niveles de resistencia proporcionalmente crecientes.

Podemos obtener una buena aproximación inicial al nivel de la resistencia con respecto a la tensión VGS, mediante la siguiente ecuación.

Funcionamiento de JFET de canal p

El diseño interno y la construcción de un JFET de canal p es exactamente idéntico a la contraparte de canal n, excepto que las regiones de materiales de tipo p y n están invertidas, como se muestra a continuación:

Las direcciones del flujo de corriente también pueden verse como invertidas, junto con las polaridades reales de voltaje VGS y VDS. En el caso de un JFET de canal p, el canal se restringirá en respuesta al aumento del potencial positivo a través de la puerta / fuente.

La notación con doble subíndice para la VDSdará lugar a un voltaje negativo para VDS, como se muestra en las características de la figura 5.12. Aquí puedes encontrarmeDSSa 6 mA, mientras que un voltaje de pellizco en VGS= + 6V.

Por favor, no se confunda debido a la presencia del signo menos de la VDS. Simplemente indica que la fuente tiene un potencial más alto que el drenaje.

Puede ver que las curvas para V altaDSlos niveles se elevan abruptamente a valores que parecen irrestrictos. Las elevaciones indicadas que son verticales simbolizan una situación de ruptura, lo que significa que la corriente a través del dispositivo de canal está completamente controlada por los circuitos externos en este momento.

Aunque esto no es evidente en la figura 5.10 para dispositivos de canal n, puede ser una posibilidad bajo voltaje suficientemente alto.

Esta región se puede eliminar si la VDS (máx.)se anota en la hoja de datos del dispositivo, y el dispositivo está configurado de manera que la V realDSEl valor es menor que este valor anotado para cualquier VGS.

Artículo anterior: 5 mejores circuitos de amplificador de 40 vatios explorados Siguiente: Hoja de datos 2N3055, Pinout, Circuitos de aplicación