El procesador MicroBlaze fue desarrollado en 2002 para integrar varias características complicadas para satisfacer la nueva y creciente demanda del mercado. Por lo tanto, el procesador MicroBlaze es un elemento esencial dentro de la cartera de gama baja de Xilinx para permitir un desarrollo de sistema más rápido que contiene Artix®-7. FPGA , Spartan®-6, Zynq®-7000 AP SoC. Este procesador es extremadamente configurable, por lo que puede usarse como un procesador integrado o microcontrolador dentro de FPGA y también como coprocesador en los SoC Zynq-7000 AP basados en ARM Cortex-A9. Este artículo proporciona información breve sobre Procesador Micro Blaze – arquitectura y trabajo con aplicaciones.

¿Qué es el procesador Microblaze?

El microprocesador suave que está diseñado principalmente para FPGA de Xilinx se conoce como procesador MicroBlaze. Este procesador simplemente se implementa dentro de la estructura lógica y de memoria de uso general de las FPGA de Xilinx. Este procesador es similar a la arquitectura DLX basada en RISC y tiene un sistema de interconexión flexible para que soporte diferentes aplicaciones embebidas. El bus de E/S principal y la interconexión AXI del MicroBlaze es un bus de transacciones mapeado en memoria con una instalación de maestro-esclavo.

MicroBlaze utiliza un bus LMB dedicado para acceder a la memoria local y proporciona almacenamiento rápido en el chip. Muchas partes de este procesador pueden ser configuradas por el usuario, como el tamaño de la memoria caché, la profundidad de la unidad de administración de memoria de canalización, los periféricos integrados y las interfaces de bus.

Características de Microblaze

los caracteristicas de microblaz e incluir lo siguiente. Tiene 32 registros de propósito general.

- Tiene palabras de instrucción de 32 bits que incluyen 2 modos de direccionamiento y 3 operandos.

- El bus de direcciones es de 32 bits.

- Tiene una tubería de 3 etapas o una tubería de 5 etapas.

- Una unidad de bloque ALU con una palanca de cambios.

- La arquitectura de Harvard incluye datos de 32 bits y bus de direcciones.

- Interfaz de datos y LMB o instrucciones de bus de memoria local.

- Interfaces de flujo AX14 y AX14.

- Unidad de punto flotante y unidad de gestión de memoria.

- Admite paso de bloqueo.

- Interfaz de depuración y rastreo.

Arquitectura Microbaze

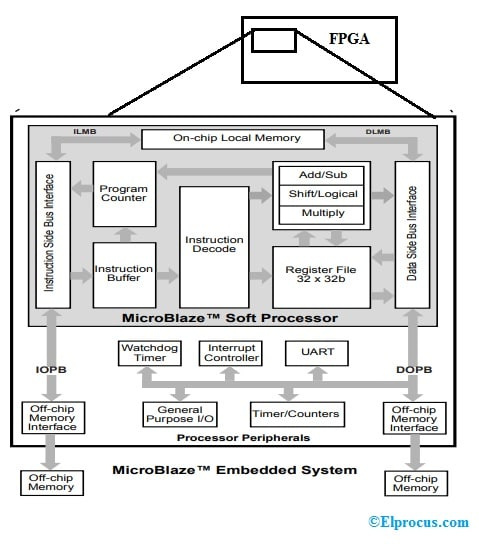

El diagrama de bloques del procesador MicroBlaze se muestra a continuación. Este procesador MicroBlaze es extremadamente personalizable y admite más de 70 opciones de diseño. Esta arquitectura muestra funciones de hardware permanentes, así como opciones configurables como la memoria caché de instrucciones o datos, la unidad de gestión de memoria, la unidad de punto flotante, etc.

Un sistema Integrado ensamblado alrededor de un procesador MicroBlaze incluye principalmente el núcleo del procesador suave MicroBlaze, la memoria local en el chip, las interconexiones de bus estándar y los periféricos OPB (bus periférico en el chip). Un sistema de procesador MicroBlaze varía principalmente desde un núcleo de procesador por una memoria local hasta un sistema grande que incluye varios MicroBlaze procesadores , memoria externa y muchos periféricos OPB.

Núcleo de procesador blando

El núcleo del procesador de software de MicroBlaze es fundamental para el sistema integrado MicroBlaze. Este es un procesador RISC de 32 bits muy rápido y eficiente que tiene las siguientes características.

- El conjunto de instrucciones es ortogonal.

- Buses de instrucción y datos separados.

- Registros de propósito general de 32 bits.

- Tiene una palanca de cambios de barril completa opcional de 32 bits.

- Interfaces incorporadas para OCM rápido o memoria en chip y OPB (bus periférico en chip) estándar de la industria de IBM.

Las implementaciones dentro de Virtex-II y los dispositivos posteriores admiten una multiplicidad de hardware.

Memoria local en chip

La memoria síncrona es una memoria local que se utiliza principalmente para permitir RAM de bloque en el chip.

Interconexiones de bus estándar

Las interfaces de bus en el lado de instrucciones y datos incluyen una interfaz para la memoria local que se llama LMB (Bus de memoria local) y una interfaz para el bus periférico en chip de IBM. Por lo tanto, podemos diseñar sistemas que se adhieran estrictamente a la arquitectura de Harvard; de lo contrario, para compartir recursos, podemos utilizar un solo OPB dentro de una combinación a través de un árbitro de bus.

El bus de memoria local ofrece una entrada segura de un solo ciclo para el bloque de RAM en el chip. Este es un protocolo de bus de maestro único muy eficiente, simple y es perfecto para interconectar memoria local rápida. El OPB u On-chip Peripheral Bus es un amplio bus multimaestro de 32 bits que es perfecto para unir periféricos y memoria exterior al núcleo del procesador MicroBlaze.

Periféricos de bus periféricos en chip

El sistema de hardware MicroBlaze se completa con periféricos OPB para proporcionar diferentes funciones como Watchdog Timer o Timebase, temporizador o contadores de propósito general, IC (controlador de interrupción), diferentes controladores como SRAM, memoria flash, memoria ZBT, BRAM, DDR, SDRAM, UART Lite , SPI, I2C, E/S de propósito general, UART 16450/550 y Ethernet 10/100 MAC. Además, también podemos agregar y definir periféricos principalmente para funciones personalizadas, de lo contrario, una interfaz para un diseño que existe en el FPGA.

Conjunto de instrucciones Microblaze

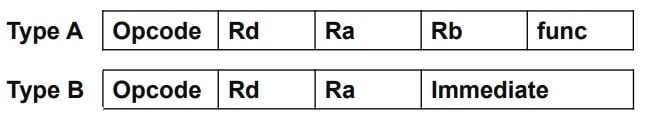

Los conjuntos de instrucciones de Microblaze son aritmética, lógica, bifurcación, carga/almacenamiento y otros. El tamaño de todas las instrucciones es fijo. Como máximo se pueden dar 3 registros como operandos. Microblaze incluye dos formatos de instrucción Tipo A y Tipo B que se muestran a continuación.

El formato de instrucción tipo A se utiliza principalmente para instrucciones de registro-registro. Por lo tanto, incluye el código de operación, el destino único y dos registros de origen. El formato de instrucción tipo B se utiliza principalmente para instrucciones de registro inmediato que incluyen el código de operación, el destino único y los registros de fuente única y una fuente de valor inmediato de 16 bits.

En los dos formatos de instrucción anteriores, el código de operación es un código de operación, Rd es un registro de destino que está codificado con 5 bits, Ra y Rb son registros de origen donde cada uno está codificado con 5 bits e Inmediato es un valor de 16 bits.

Instrucciones aritméticas

Las instrucciones aritméticas tipo A y tipo B se dan a continuación.

Escribe un

|

AGREGAR Rd, Ra, Rb agregar |

Rd = Ra+Rb, bandera de acarreo afectada |

|

AGREGAR K Rd, Ra, Rb Agregar y mantener llevar |

Rd = Ra+Rb, la bandera de acarreo no se ve afectada |

| RSUB Rd, Ra, Rb resta inversa |

Rd = R-Rb, la bandera de acarreo no se ve afectada |

Tipo B

|

AGREGAR I Rd, Ra, Imm añadir inmediato |

Rd = Ra+signExtend32 (Imm) |

|

AGREGAR IK Rd, Ra, Imm agregar inmediato y mantener llevar |

Rd = Ra+ signExtend32 (Imm) |

| RSUBIK Calle, Ra, Imm resta inversa con inmediata |

Rd = Ra+ signExtend32 (Imm) -Ra |

| Calle SRA, Ra desplazamiento aritmético a la derecha |

Rd = (Ra>>1) |

Instrucciones lógicas

Las instrucciones lógicas de tipo A y tipo B se dan a continuación.

Escribe un

|

O Rd, Ra, Rb lógico o |

Rd = Ra| Rb |

|

Y Rd,Ra,Rb Adición lógica |

Rd = Ra y Rb |

| XOR Rd, Ra, Rb xor logoico |

Rd = Rb ^ Rb |

| ANDN Calle, Ra, Rb lógico y no |

Rd = Ra & (Rb) |

Tipo B

|

ORI Rd, Ra, Imm OR lógico con inmediato |

Rd = Ra | signExtend32 (Imm) |

| ANDI Rd, Ra, Imm AND lógico con inmediato |

Rd = Ra & signExtend32 (Imm) |

| XORI Rd, Ra, Imm XOR logoical con inmediato |

Rd = Ra ^ signExtend32 (Imm) |

| ANDNI Rd, Ra, Imm Lógico Y NO con inmediato |

Rd = Ra & (signExtend32 (Imm)) |

Instrucciones de bifurcación: incondicional

Modificar el registro del contador de programa

| BRID Inm sucursal inmediata con demora inmediata |

PC = PC+ signExtend32 (Imm) permitir la ejecución de la ranura de retraso |

| BRLID Rd, Imm bifurcación y enlace inmediato con retardo inmediato (llamada de función) |

Rd = CP PC = PC+& signExtend32 (Imm) permitir la ejecución de la ranura de retraso |

| RTSD Ra, Imm retorno de subrutina |

PC = Ra + signExtend32 (Imm) permitir la ejecución de la ranura de retraso |

| RTID Ra, Imm regreso de interrupción |

PC = Ra + signExtend32 (Imm) permitir la ejecución de la ranura de retraso establecer la habilitación de interrupción en MSR |

Instrucciones de bifurcación: incondicional1

Cambiar el registro del contador de programa cuando se cumple una condición

| BEQI Ra, Imm rama si es igual |

PC = PC+ signExtend32 (Imm) Si Ra = = 0 |

| MASH Ra, Imm rama si no es igual |

Rd = CP PC = PC+& signExtend32 (Imm) Si Ra! = 0 |

Instrucciones de bifurcación: incondicional2

Cambiar el registro del contador de programa cuando se cumple una condición

| BLTI Ra, Imm rama si es inferior a |

PC = PC+ signExtend32 (Imm) Si Ra < 0 |

| BLEI Ra, Imm rama si menor igual que |

Rd = CP PC = PC+& signExtend32 (Imm) Si Ra!< = 0 |

| BGTI Ra, Imm rama si es mayor que |

PC = PC+ signExtend32 (Imm) Si Ra! > 0 |

| BGEI Ra, Imm rama si mayor igual que |

PC = PC+signExtend32 (Imm) Si Ra!>= 0 |

Instrucciones de carga/almacenamiento -Tipo A

| LW Rd, Ra, Rb Cargar palabra |

Dirección = Ra+Rb Rd = *Dirección |

| Calle SW, Ra, Rb Palabra de la tienda |

Dirección – Ra+Rb *Dirección = Calle |

Tipo B

| LWI Rd, Ra, Imn Cargar palabra inmediata |

Dirección = Ra + signExtend32 (Imm) Rd = *Dirección |

| SW Rd, Ra, Imm Almacenar palabra inmediata |

Dirección = Ra + signExtend32 (Imm) *Dirección = Calle |

Otras instrucciones

| IMM, Imm inmediato |

Extienda el Imm de una instrucción de tipo B anterior a 32 bits. |

| MFS Rd, Sa Mover desde registro de propósito especial |

Rd = sa Sa- registro de propósito especial, operando fuente

|

| MTS SD, Ra Mover al registro de propósito especial |

SD = Ra Sd - registro de propósito especial, operando de destino |

Registros

La arquitectura del procesador MicroBlaze es completamente ortogonal e incluye registros de propósito general de 32 bits y registros de propósito especial de 32 bits, como contador de programa y registro de estado de la máquina.

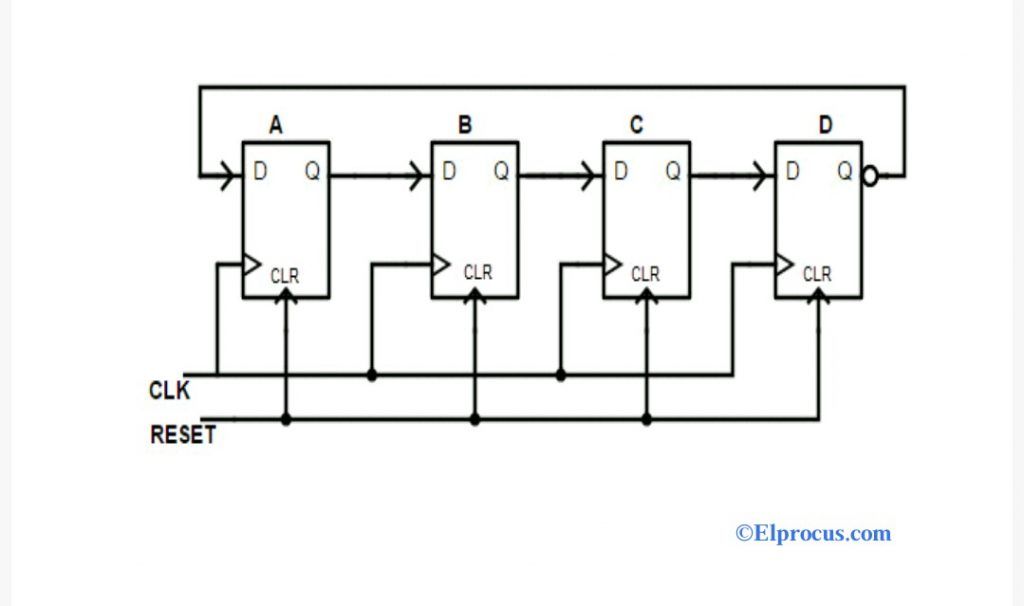

Arquitectura de tubería

MicroBlaze utiliza una arquitectura de canalización de 3 etapas que incluye las etapas de obtención, decodificación y finalización. Automáticamente, el reenvío de datos, las ramificaciones y la parada de la tubería se determinan dentro del hardware.

Cargar o almacenar arquitectura

MicroBlaze admite memoria en tres tamaños de datos: 8 bits (Byte), 16 bits (Media palabra) y 32 bits (Palabra). Por lo tanto, los accesos a la memoria siempre están alineados con el tamaño de los datos. Este es un procesador Big-Endian que utiliza la dirección de la dirección Big-Endian, así como las convenciones de etiquetado una vez que accede a la memoria.

Interrupciones

Una vez que se produce una interrupción, este procesador finalizará la ejecución actual para administrar la solicitud de interrupción a través de la bifurcación para interrumpir la dirección del vector y almacenar la dirección de instrucción que debe ejecutarse. Este procesador detendrá futuras interrupciones borrando el indicador IE (Habilitación de interrupción) dentro del MSR (Registro de estado de la máquina).

¿Cómo funciona Microblaze?

El procesador MicroBlaze admite un ancho de bus de 32 bits y este núcleo de procesador es un motor basado en RISC que incluye un archivo de registro basado en LUT RAM de 32 bits a través de instrucciones separadas para el acceso a la memoria y los datos.

Este procesador simplemente admite BlockRAM en chip y memoria externa. Similar al IBM PowerPC; todos los periféricos utilizan el bus CoreConnect OPB similar; los periféricos del procesador se combinan bien con PowerPC en Virtex-II Pro.

El procesador MicroBlaze ofrece total flexibilidad para elegir la combinación de funciones de memoria, periféricos e interfaz que le brindarán el sistema preciso que necesita en un solo FPGA con un costo menor.

Diferencia B/N Microblaze Vs Risc-V

los diferencia entre MicroBlaze y RISC v Incluya lo siguiente.

|

Microblaze |

Riesgo-V |

| Es un núcleo de microprocesador suave diseñado principalmente para Xilinx FPGA.

|

RISC-V es una arquitectura de conjunto de instrucciones arraigada en los principios de RISC.

|

| Utiliza la arquitectura Harvard RISC. | Utiliza arquitectura de conjunto de instrucciones. |

| Su licencia es propietaria (Xilinx) | Su licencia es de código abierto. |

| La profundidad de la tubería es de 3 o 5. | La profundidad de la tubería es 5. |

| Su rendimiento es de 280 DMIPs. | Su rendimiento es de 250 DMIPs. |

| Su velocidad es de 235 MHz. | Su velocidad es de 250 MHz. |

| Tiene 1027 LUT. | Tiene 4125 LUT. |

| La implementación de la tecnología utilizada es Xilinx FPGA. | La implementación de la tecnología utilizada es FPGA/ASIC. |

Ventajas de Microblaze

los ventajas de microblaze Incluya lo siguiente.

- es economico

- Es altamente configurable.

- Su rendimiento es alto en comparación con ARM.

- Es compatible con un kit de desarrollo integrado.

- es un suave microprocesador centro.

- Para ayudarlo a organizar rápidamente su aplicación, este procesador incluye tres configuraciones fijas que están relacionadas con las conocidas clases de procesadores: microcontrolador, en tiempo real y procesador de aplicaciones.

Aplicaciones Microblaze

los aplicaciones de microblaze Incluya lo siguiente.

- Este procesador cumple con muchos requisitos de aplicaciones diferentes, como industriales, automotrices, médicas y de consumo, etc.

- Las aplicaciones de MicroBlaze van desde máquinas de estado simples basadas en software hasta controladores complejos utilizados en aplicaciones integradas o dispositivos basados en Internet.

- Está optimizado para aplicaciones integradas como control industrial, automatización de oficinas y automoción.

- El MicroBlaze es capaz de comunicarse con un gran conjunto de periféricos para adaptarse a aplicaciones de mediana escala.

- La naturaleza suave de este procesador lo hace personalizable para diferentes aplicaciones donde los diseñadores pueden intercambiar características por tamaño para cumplir con los objetivos de precio y rendimiento para aplicaciones médicas, automotrices, industriales y de seguridad.

Por lo tanto, todo esto se trata una descripción general del Microblaze procesador. Se trata de un núcleo de procesador de software RISC programable de 32 bits con todas las funciones. Este procesador cumple con diferentes requisitos dentro de diferentes campos, como los mercados de infraestructura de consumo, médico, industrial, automotriz y de comunicaciones. Es extremadamente configurable, por lo que se usa como procesador incorporado o microcontrolador dentro de FPGA, de lo contrario, como coprocesador para ARM. Aquí hay una pregunta para ti, ¿qué es FPGA?