La ECL (lógica acoplada al emisor) fue inventada por primera vez en IBM en agosto de 1956 por Hannon S. Yourke. Esta lógica también se conoce como lógica de modo actual, utilizada en las computadoras de IBM 7090 y 7094. La familia ECL es muy rápida en comparación con lógica digital familias Generalmente, esta familia lógica proporciona un retardo de propagación de menos de 1 ns. Es una familia lógica basada en transistores de unión bipolar. Es el circuito familiar lógico más rápido al que se puede acceder para diseñar un sistema lógico convencional. Este artículo analiza una descripción general de un circuito lógico acoplado emisor , trabajando con aplicaciones.

¿Qué es la lógica acoplada de emisor?

La lógica acoplada por emisor es la mejor BJT -familia lógica basada en utilizada en el diseño de sistemas lógicos convencionales. A veces, también se denomina lógica de modo actual, que es una tecnología digital de muy alta velocidad. En general, ECL se considera como el circuito integrado lógico más rápido donde logra su operación de alta velocidad mediante el uso de una oscilación de voltaje muy pequeña y también evitando que los transistores entren en la región de saturación.

Una implementación de ECL utiliza un voltaje de suministro positivo que se conoce como PECL o ECL con referencia positiva. En las primeras puertas ECL, se usa un suministro de voltaje negativo debido a la inmunidad al ruido. Después de eso, ECL con referencia positiva se hizo muy famoso debido a sus niveles lógicos más compatibles en comparación con las familias lógicas TTL.

La lógica acoplada al emisor disipa una gran cantidad de energía estática, sin embargo, su consumo general de corriente es bajo en comparación con CMOS a altas frecuencias. Por lo tanto, ECL es principalmente beneficioso en circuitos de distribución de reloj y aplicaciones basadas en alta frecuencia.

Características de la lógica acoplada del emisor

Las características de ECL harán que se utilicen en muchas aplicaciones basadas en alto rendimiento.

- ECL proporciona dos salidas que siempre son complementarias entre sí porque la operación del circuito se basa en un amplificador diferencial.

- Esta familia lógica es principalmente adecuada para métodos de fabricación monolíticos porque los niveles lógicos son una función de las relaciones de resistencia.

- Los dispositivos de la familia ECL generan la salida correcta y complementaria de la función propuesta sin utilizar inversores externos. En consecuencia, disminuye el conteo de paquetes y los requisitos de energía y también disminuye los problemas que ocurren debido a los retrasos de tiempo.

- Los dispositivos ECL en diseño de amplificador diferencial ofrecen una amplia flexibilidad de rendimiento, por lo que los circuitos ECL permiten su uso tanto como circuitos digitales como lineales.

- El diseño de la puerta ECL normalmente tiene una impedancia de entrada alta y baja, lo que es extremadamente propicio para lograr una gran distribución y capacidad de accionamiento.

- Los dispositivos ECL generan un drenaje de corriente constante en la fuente de alimentación para simplificar el diseño de la fuente de alimentación.

- Los dispositivos de ECL que incluyen salidas de emisor abierto simplemente les permiten incluir capacidad de accionamiento de línea de transmisión.

Circuito Lógico Acoplado por Emisor

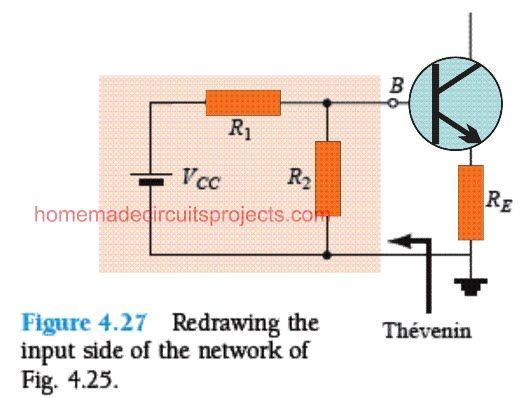

A continuación se muestra el circuito lógico acoplado por emisor para el inversor, que está diseñado con resistencias y transistores. En este circuito, los terminales emisores de dos transistores simplemente se conectan a la resistencia limitadora de corriente RE que se utiliza para evitar que el transistor entre en saturación. Aquí, la salida del transistor se toma del terminal del colector en lugar del terminal del emisor. Este circuito proporciona dos salidas Vout (salida inversora) y Vout2 (salida no inversora) y el terminal de entrada como Vin donde se proporciona una entrada alta o baja. +Vcc = 5V.

¿Cómo funciona la lógica acoplada del emisor?

El funcionamiento de la lógica acoplada al emisor es que cada vez que la entrada ALTA se le da al circuito ECL, entonces encenderá el transistor 'Q1' y apagará el transistor Q2, pero el transistor Q1 no está saturado. Entonces, esto llevará la salida VOUT2 a ALTO y el valor de la salida VOUT1 será BAJO debido a la caída dentro de R1.

De manera similar, cuando el valor VIN dado a ECL es BAJO, entonces hará que el transistor Q1 se apague y el transistor Q2 se encienda. Entonces, el transistor Q2 no se saturará. Por lo tanto, hará que la salida VOUT1 tenga un valor ALTO y el valor de salida VOUT2 será bajo debido a la caída dentro de la resistencia R2.

Veamos cómo se enciende y apaga el transistor Q1 y Q2 cuando se aplica un voltaje.

Los dos transistores como Q1 y Q2 en este circuito están conectados como un amplificador diferencial por una resistencia de emisor común.

Los suministros de voltaje para este circuito de ejemplo son VCC = 5,0, VBB = 4,0 y VEE = 0 V. Los valores de entrada de nivel ALTO y BAJO se definen simplemente como 4,4 V y 3,6 V. En realidad, este circuito genera una salida BAJA y niveles ALTOS que son 0,6 voltios más altos; sin embargo, esto se corrige dentro de los circuitos ECL reales.

Una vez que Vin es ALTO, el transistor Q1 se enciende, sin embargo, no está saturado y el transistor Q2 se apaga. Entonces, el voltaje de salida como VOUT2 se eleva a 5 V a través de la resistencia R2 y se puede demostrar que la caída de voltaje en la resistencia R1 es de aproximadamente 0,8 V, por lo que VOUT1 = 4,2 V (BAJO). Además, VE = VOUT1 – VQ1 => 4,2 V – 0,4 V = 3,8 V cuando el transistor Q1 se enciende por completo.

Una vez que Vin esté BAJO, el transistor Q2 se encenderá, pero no se saturará y el transistor Q1 se apagará. Por lo tanto, VOUT1 se lleva a 5,0 V usando una resistencia R1 y se puede demostrar que VOUT2 es de 4,2 V. También VE => VOUT2 – VQ2 => 4,2 V – 0,8 V => 3,4 V cuando el transistor Q2 está encendido.

En ECL, los dos transistores nunca están saturados como t Las oscilaciones de voltaje de entrada / salida son bastante pequeñas, como 0.8v y la impedancia de entrada es alta y la resistencia de salida es baja. Esto ayuda a ECL a operar más rápido con un menor tiempo de retraso de propagación.

Circuito de compuerta OR/NOR lógico acoplado con emisor de dos entradas

A continuación se muestra el circuito de compuerta OR/NOR lógico acoplado con dos emisores de entrada. Este circuito está diseñado modificando el circuito inversor anterior. La modificación consiste en agregar un transistor adicional en el lado de entrada.

El funcionamiento de este circuito es muy sencillo. Cuando las entradas aplicadas en los transistores Q1 y Q2 son bajas, la salida 1 (Vout1) tendrá un valor ALTO. Entonces, este Vout1 corresponde a la salida de la puerta NOR.

Simultáneamente, si el transistor Q3 está encendido, hará que la segunda salida (Vout2) sea ALTA. Entonces, esta salida de Vou2 corresponde a la salida de la puerta OR.

De la misma manera, si las entradas de los transistores Q1 y Q2 son ALTAS, entonces encenderá los transistores Q1 y Q2 y proporcionará la salida baja en el terminal VOUT1.

Si el transistor Q3 se apaga durante esta operación, proporcionará una salida alta en el terminal VOUT2. Entonces, la tabla de verdad para la puerta OR/NOR se muestra a continuación.

|

Entradas |

Entradas | O |

NI |

|

A |

B | Y | Y |

|

0 |

0 | 0 | 1 |

|

0 |

1 | 1 |

0 |

| 1 | 0 | 1 |

0 |

| 1 | 1 | 1 |

0 |

Características de la lógica acoplada al emisor

Las características de ECL incluyen lo siguiente.

- En comparación con TTL, ECL tiene un tiempo de propagación más rápido que oscila entre 0,5 y 2 ns. Pero, la disipación de potencia lógica acoplada al emisor es mayor en comparación con TTL como 30 mW.

- Los voltajes de E/S de ECL tienen una pequeña oscilación como 0,8.

- La impedancia de entrada de ECL es alta y la resistencia de salida es baja; en consecuencia, el transistor cambia sus estados muy rápidamente.

- La capacidad de distribución de ECL es alta y los retrasos de puerta son bajos.

- La lógica o/p de ECL cambia de un estado BAJO a ALTO, pero los niveles de voltaje para estos estados variarán entre TTL y EC.

- La inmunidad al ruido de ECL es de 0,4 V.

Ventajas y desventajas

los ventajas de la lógica acoplada por emisor se discuten a continuación.

- El fanout de ECL es 25, que es mejor en comparación con TTL y es bajo en comparación con CMOS.

- El tiempo de retardo de propagación promedio de ECL es de 1 a 4 ns, que es mejor en comparación con CMOS y

- TTL. Por lo tanto, se denomina familia lógica más rápida.

- Cuando los BJT en el emisor se acoplaron puertas lógicas trabajan en la región activa, entonces tienen la velocidad máxima en comparación con todas las familias lógicas.

- Las puertas ECL generan salidas complementarias.

- No hay picos de conmutación de corriente en los cables de alimentación.

- Las salidas se pueden acoplar de forma conjunta para proporcionar la función OR cableada.

- Los parámetros de ECL no cambian mucho con la temperatura.

- El no. de funciones accesibles desde un único chip es alto.

los desventajas de la lógica acoplada por emisor se discuten a continuación.

- Tiene un margen de ruido extremadamente bajo, es decir, ±200 mV.

- La disipación de energía es alta en comparación con otras puertas lógicas.

- Para interactuar con otras familias lógicas, se necesitan cambiadores de nivel.

- Fanout limita la carga capacitiva.

- En comparación con TTL , las puertas ECL son caras.

- En comparación con CMOS y TTL, la inmunidad al ruido ECL es peor.

Aplicaciones

Las aplicaciones de la lógica acoplada por emisor incluyen lo siguiente.

- La lógica acoplada por emisor se utiliza como tecnología lógica e interfaz dentro de dispositivos de comunicación de velocidad extremadamente alta, como interfaces de transceptor de fibra óptica, redes Ethernet y ATM (modo de transferencia asíncrono).

- ECL es una familia lógica basada en BJT donde su operación de alta velocidad se puede lograr utilizando una oscilación de voltaje relativamente pequeña y evitando que los transistores se muevan hacia la región de saturación.

- ECL se utiliza para hacer los circuitos ASLT dentro de IBM 360/91.

- ECL evita la utilización de transistores apilados mediante el uso de una i/p de polarización de un solo extremo y una retroalimentación positiva entre los transistores primario y secundario para lograr una función de inversor.

- ECL se utiliza en electrónica de velocidad extremadamente alta.

Así, esto es una descripción general de una lógica acoplada de emisor o ECL: circuito, funcionamiento, funciones, características y aplicaciones. ECL es la familia lógica más rápida basada en BJT en comparación con otras familias lógicas digitales. Alcanza su máxima velocidad de operación usando una pequeña oscilación de voltaje y evitando que los transistores se muevan hacia la región de saturación. Esta familia lógica proporciona un increíble retraso de propagación de 1 ns y en las últimas familias ECL, este retraso se reduce. Aquí hay una pregunta para usted, ¿cuál es un nombre alternativo para ECL?

![Circuito convertidor de 24 V a 12 V CC [con regulador de conmutación]](https://electronics.jf-parede.pt/img/3-phase-power/F1/24-v-to-12-v-dc-converter-circuit-using-switching-regulator-1.jpg)