En nuestro día a día, solemos comunicarnos con otros con frecuencia utilizando múltiples tipos de sistemas de comunicación . Este sistema de comunicación se puede clasificar en diferentes tipos, como un sistema de comunicación por radio, sistema de telecomunicaciones, Sistema de comunicación inalámbrica , Sistema de comunicación óptica, etc. Para que todos estos sistemas de comunicación funcionen de manera eficiente, necesitamos algunos sistemas de control, como un bucle de bloqueo de fase, control cooperativo, control en red, etc.

¿Qué es el bucle de bloqueo de fase (PLL)?

El bucle de bloqueo de fase se utiliza como sistema de control para controlar diferentes operaciones en muchos sistemas de comunicación, computadoras y muchos aplicaciones electronicas . Se utiliza para generar una señal de salida que tiene una fase relacionada con la fase de la señal de entrada.

Hay diferentes tipos de PLL, como PLL analógico o lineal, PLL digital, PLL de software, PLL neuronal y todos los PLL digitales.

Operación de bucle de bloqueo de fase

En los sistemas de comunicación, la operación PLL se puede explicar considerando sistemas analógicos y digitales .

Lazo de fase analógica en sistemas de comunicación

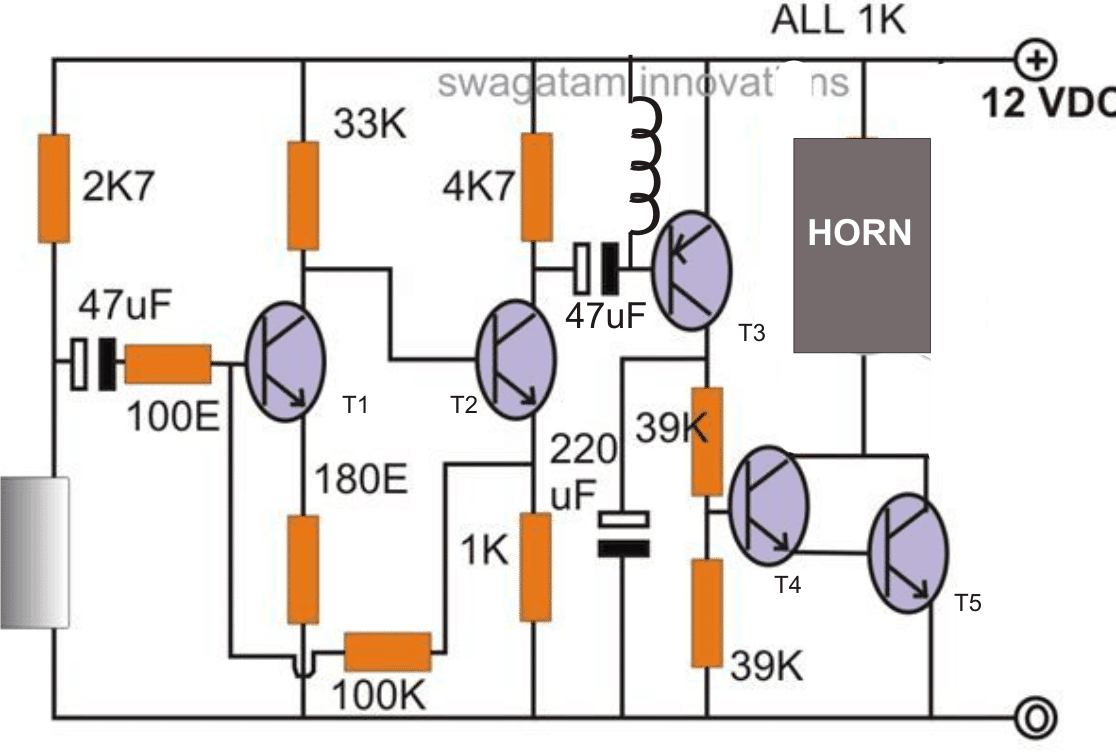

Básicamente, PLL es una forma de servo bucle y un PLL básico consta de tres elementos principales, a saber, comparador / detector de fase, filtro de bucle y oscilador controlado por voltaje .

Bucle de fase bloqueada

El concepto principal detrás de la operación PPL es la comparación de las fases de dos señales (generalmente se comparan las fases de las señales de entrada y salida). Por tanto, la diferencia de fase entre la señal de entrada y salida se puede utilizar para controlar la frecuencia del bucle. Aunque el análisis matemático es muy complicado, el funcionamiento del PLL es muy sencillo.

En muchos sistemas de comunicación, PLL se utiliza para diferentes propósitos:

- Para seguir la fase o modulación de frecuencia , se utiliza como demodulador.

- Para rastrear o sincronizar las dos señales con diferentes frecuencias.

- Para eliminar ruidos grandes de señales pequeñas.

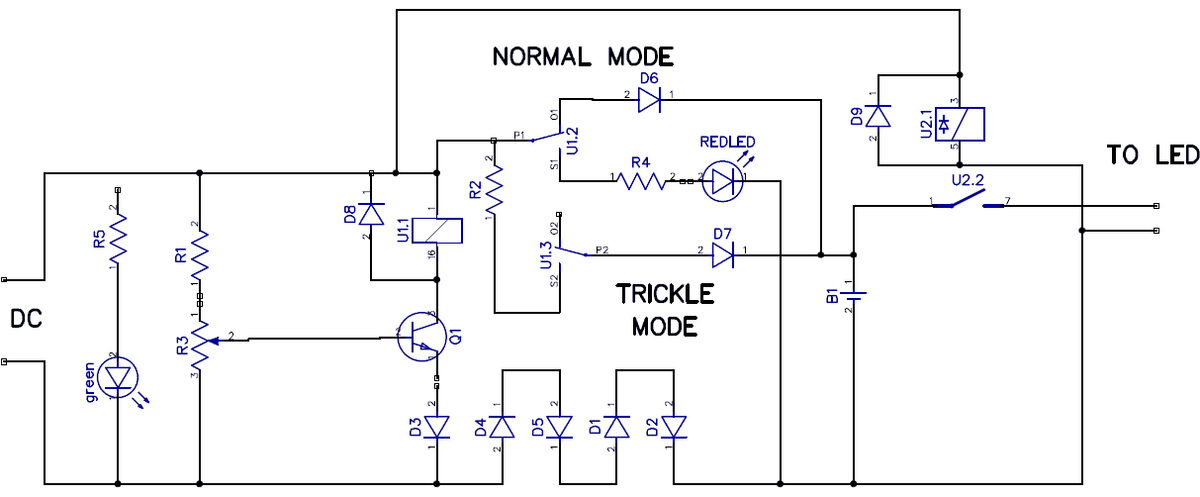

La siguiente figura muestra el PLL básico que consta de detector de fase, oscilador controlado por voltaje (VCO) y filtro de bucle.

El oscilador controlado por voltaje de PLL produce una señal y esta señal del VCO se envía al detector de fase. El detector de fase compara esta señal con la señal de referencia y, por lo tanto, produce un voltaje de error o voltaje diferencial. Esta señal de error del detector de fase se alimenta al filtro de paso bajo para eliminar los elementos de alta frecuencia de la señal, si los hay, y para controlar muchas propiedades del bucle. Luego, la salida del filtro de bucle se alimenta para suministrar el voltaje de sintonización para el terminal de control del oscilador controlado por voltaje.

El cambio en este voltaje de sintonía se detecta para reducir la diferencia de fase entre las dos señales (entrada y salida) y, por lo tanto, la frecuencia entre ellas. Inicialmente, el PLL no se bloquea y el voltaje de error arrastra la frecuencia del VCO hacia la referencia hasta que el error no se puede reducir más y luego el bucle se bloquea.

El error real entre las dos señales (entrada y salida) se reduce a niveles muy pequeños. usando un amplificador entre el oscilador controlado por voltaje y un detector de fase. Si el PLL está bloqueado, se producirá un voltaje de error de estado estable. Este voltaje de error de estado estable representa que no hay cambio de diferencia de fase entre la señal de referencia y VCO. Por tanto, podemos decir que la frecuencia de las dos señales (señales de entrada y salida) es exactamente la misma.

Bucle de bloqueo de fase digital en sistemas de comunicación

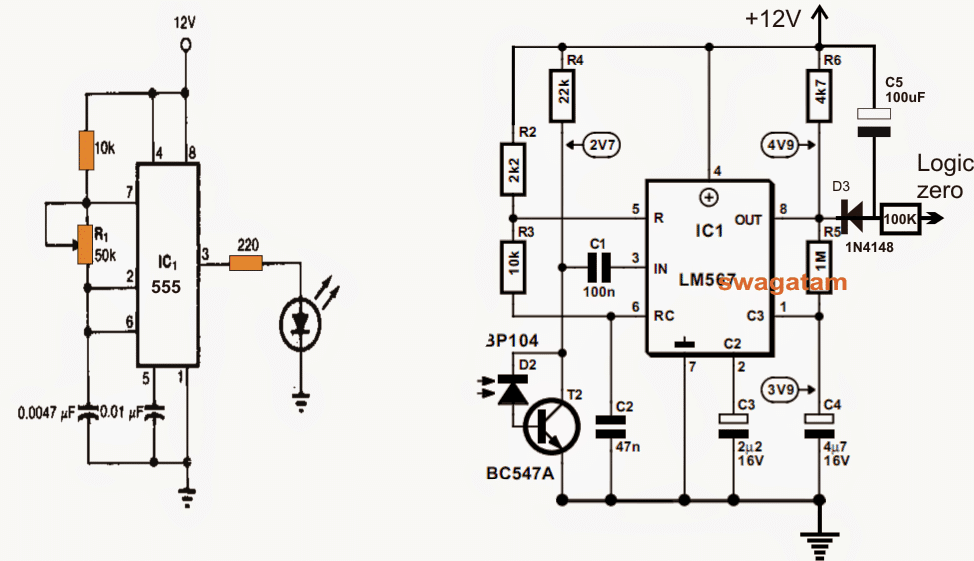

En general, los PLL analógicos constan de un detector de fase analógica, un oscilador controlado por voltaje y un filtro de paso bajo. De manera similar, el bucle bloqueado de fase digital consta de un detector de fase digital, un registro de desplazamiento en serie , una señal de reloj local estable.

Bucle de bloqueo de fase digital

Las muestras de entrada digital se extraen de la señal recibida y estas muestras son recibidas por el registro de desplazamiento en serie, que es impulsado por pulsos de reloj suministrados por una señal de reloj local. Se utiliza un circuito corrector de fase que toma el reloj local para regenerar una señal de reloj estable en fase con la señal recibida mediante un ajuste de fase lento para que coincida con la fase de la señal recibida.

Este ajuste puede realizarse basándose en una muestra de alta velocidad de cada bit utilizando una lógica de corrección. La muestra de la señal recibida obtenida mediante el muestreo de la señal recibida a la velocidad del reloj local se coloca en el registro de desplazamiento.

El ajuste de fase requerido se puede detectar observando el conjunto de muestras de la señal recibida. Se dice que los dos relojes están en fase si y solo si el centro del bit recibido se encuentra en el centro del registro de desplazamiento. El ajustador de fase está diseñado para compensar si el reloj regenerado se retrasa o adelanta la señal de referencia.

Aplicación de bucle de bloqueo de fase

- Los PLL se utilizan con frecuencia con fines de sincronización y para sincronización de bits, sincronización de símbolos, demodulación coherente y extensión de umbral en la comunicación espacial.

- Las señales de frecuencia modulada se pueden demodular utilizando el PLL.

- La nueva frecuencia que es un múltiplo de la frecuencia de referencia en transmisores de radiocomunicación , y sintetizado manteniendo la estabilidad de la frecuencia de referencia con la nueva frecuencia se puede lograr mediante PLL.

- Existen numerosas aplicaciones para PLL en muchos sistemas de comunicación, computadoras y muchos circuitos electrónicos .

- La siguiente aplicación de PLL describe el uso de PLL como voltaje para convertidor de frecuencia .

Convertidor de voltaje a frecuencia (VFC) usando un PLL

En los sistemas de comunicación, se requiere enviar señales (considere una señal analógica aquí) a una larga distancia con total precisión. Para ello, se utiliza un convertidor de tensión a frecuencia, ya que es fácil enviar una señal de frecuencia sin provocar interferencias a larga distancia mediante aisladores ópticos, líneas coaxiales o de par trenzado, radioenlaces, enlaces de fibra óptica .

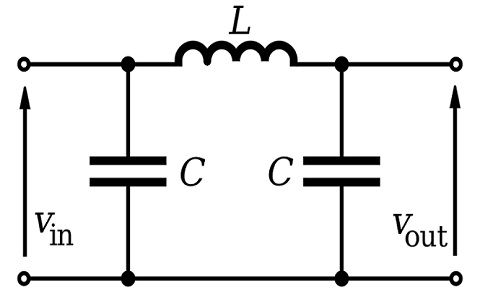

Hay dos tipos de convertidores de voltaje a frecuencia: tipo multivibrador VFC y tipo de saldo de carga VFC.

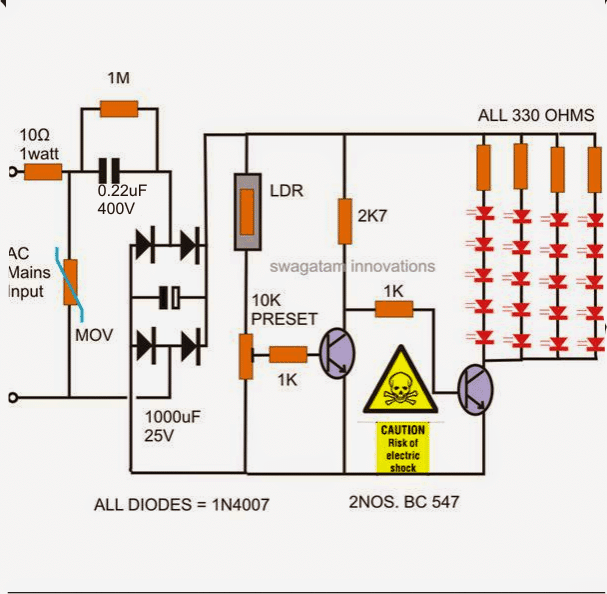

Multivibrador tipo VFC

VFC multivibrador

En el multivibrador tipo VFC, el condensador se carga y descarga utilizando la corriente obtenida del voltaje de entrada. Se proporciona una entrada de referencia estable para establecer los umbrales de conmutación, y la frecuencia de salida es proporcional al voltaje de entrada y tiene una relación de marca-espacio unitaria.

Tipo de saldo de carga VFC

Balance de carga VFC

El balance de carga VFC consta de un integrador, un comparador y una fuente de carga de precisión, siempre que se le da una entrada al integrador, se carga y si la salida de este integrador alcanza el umbral del comparador, entonces la fuente de carga se activa y carga fija se elimina del integrador. La tasa de carga eliminada debe ser igual a la tasa de carga suministrada, de modo que la frecuencia de activación de la fuente de carga y la entrada al integrador sean proporcionales entre sí.

Por tanto, este artículo ofrece una breve descripción sobre sistema de bucle de bloqueo de fase en el sistema de comunicación. Además, este artículo se puede ampliar técnicamente en función de sus sugerencias y consultas. Por lo tanto, puede contactarnos para cualquier asistencia técnica publicando sus comentarios a continuación.