La publicación detalla los diferentes métodos para configurar un circuito de corrección de factor de potencia o un circuito PFC en diseños SMPS, y explica las opciones de mejores prácticas para estas topologías para que cumplan con las pautas modernas de restricción de PFC.

Diseñar circuitos de suministro de energía eficientes nunca ha sido fácil, sin embargo, con el paso del tiempo los investigadores han podido resolver la mayoría de los problemas preocupantes y, en la misma línea, los diseños SMPS modernos también se están optimizando con los mejores resultados posibles, gracias a los estándares regulatorios emergentes que jugaron un papel importante en la implementación de parámetros de calidad más estrictos para las unidades de suministro de energía modernas.

Directrices de PFC

Las restricciones modernas de calidad del suministro de energía se establecen de manera bastante agresiva, colectivamente por esfuerzos de los fabricantes, proveedores y otros órganos de gobierno interesados.

Entre los muchos parámetros de calidad establecidos para los diseños modernos de fuentes de alimentación, la corrección de corrección del factor de potencia (PFC), que en realidad tiene la forma de cancelación de armónicos, ha sido declarada como un requisito obligatorio por las reglas IEC 61000-3-2.

Debido a esto, los diseñadores se ven obligados a enfrentar desafíos más difíciles en el diseño de etapas de corrección del factor de potencia en sus diseños de fuentes de alimentación para cumplir con estas estrictas leyes modernas, y con fuentes de alimentación cada vez más formidables con sus especificaciones y rango de aplicación, estructurando circuitos PFC adecuados. no es más fácil para los muchos fabricantes en la arena.

Los tutoriales presentados están especialmente dedicados a todas aquellas asociaciones y profesionales que se dedican a la fabricación o diseño de SMPS flyback para facilitarles los diseños y cálculos de PFC más ideales según sus requisitos individuales.

Las discusiones incluidas en estos tutoriales lo ayudarán a diseñar circuitos PFC incluso para unidades significativamente grandes en el rango de hasta 400 vatios, 0,75 amperios.

Los lectores también tendrán la oportunidad de aprender sobre la selección de convertidores aislados de una sola etapa que también incluyen controladores LED. El tutorial de diseño paso a paso e instrucciones junto con las comparaciones de nivel de sistema, los muchos diseñadores involucrados activamente en el campo de la electrónica de potencia se iluminarán para seguir con el enfoque más óptimo para sus necesidades de aplicación específicas

Objetivo de corrección del factor de potencia

La optimización del circuito de corrección del factor de potencia dentro de las unidades SMPS (fuente de alimentación conmutada) modernas podría evolucionar en el pasado reciente debido a la llegada de una serie de circuitos integrados (IC) relevantes avanzados, que han hecho posible establecer diferentes diseños de PFC con características específicas modos de operación y con capacidad de manejo de desafíos individuales.

Con el aumento en la gama de topologías SMPS, la complejidad en el diseño y la implementación de PFC también se ha agravado en la actualidad.

En el primer tutorial aprenderemos sobre los detalles operativos del diseño, que es el preferido por los profesionales de las correcciones.

Básicamente, la corrección del factor de potencia ayuda a optimizar la corriente de entrada dentro de las fuentes de alimentación fuera de línea para que puedan mejorar la potencia real de la entrada de red disponible.

De acuerdo con el requisito normal, un aparato eléctrico dado debe emularse a sí mismo como una carga que tiene una resistividad pura, de modo que le permita tener un consumo de energía reactiva cero.

Esta condición da como resultado la generación de corrientes armónicas de entrada casi nulas, es decir, permite que la corriente consumida esté perfectamente en línea en fase con la tensión de alimentación de entrada que normalmente tiene forma de onda sinusoidal.

Este logro facilita que el aparato consuma la “energía real” de la red en los niveles más óptimos y eficientes, lo que a su vez redunda en minimizar el desperdicio de electricidad y aumentar su eficiencia.

Este uso efectivo de la electricidad no solo ayuda a que el aparato se presente de la manera más eficiente, sino también a las empresas de servicios públicos y al equipo de capital involucrado en el proceso.

Además, la característica anterior permite que las líneas eléctricas estén libres de armónicos y la interferencia resultante a través de los dispositivos dentro de la red.

Además de las ventajas mencionadas anteriormente, incluir un PFC en las unidades de suministro de energía modernas también es para cumplir con los requisitos reglamentarios establecidos en Europa y Japón con la IEC61000-3-2, que todos los equipos eléctricos deben calificar.

La condición mencionada anteriormente ha sido regulada para la mayoría de los aparatos electrónicos que pueden tener una potencia nominal superior a 75 vatios según los estándares de equipos de Clase D o que son incluso más altos, especificando la amplitud más alta de los armónicos de frecuencia de línea que van hasta el armónico 39.

Además de estos estándares, el PFC también se emplea para garantizar otras eficiencias, como Energy Star 5.0 vital para computadoras y Energy Star 2.0 para sistemas de fuentes de alimentación y televisores desde 2008.

Definición de factor de potencia

La corrección del factor de potencia o PFC puede definirse como la relación entre la potencia real y la potencia aparente, y expresarse como:

PF = potencia real / potencia aparente, donde la potencia real se expresa en

Watts, mientras que la potencia aparente se expresa en VA.

En esta expresión, la potencia real se determina como el promedio del producto instantáneo de la corriente y el voltaje a lo largo de una fase o ciclo, mientras que la potencia aparente se considera como el valor RMS de la corriente por el voltaje.

Esto sugiere que siempre que las contrapartes de corriente y voltaje sean sinusoidales y estén en fase entre sí, el factor de potencia resultante es 1.0.

Sin embargo, en una condición en la que los parámetros de voltaje y corriente son sinusoidales pero no en fase, da lugar a un factor de potencia que es el coseno del ángulo de fase.

Las condiciones del factor de potencia descritas anteriormente se aplican en los casos en que el voltaje y la corriente son ondas sinusoidales puras, junto con una situación en la que la carga que la acompaña está formada por componentes resistivos, inductivos y capacitivos que pueden ser todos de naturaleza no lineal, que no se ajusta con los parámetros de voltaje y corriente de entrada.

Las topologías SMPS típicamente introducen impedancia no lineal en la línea principal debido a la naturaleza de sus circuitos explicada anteriormente.

Cómo funciona SMPS

Un circuito SMPS básicamente incluye una etapa rectificadora en la entrada que podría ser una media onda o un rectificador de onda completa y un condensador de filtro complementario para mantener el voltaje rectificado a través de él hasta el nivel máximo de la onda sinusoidal de suministro de entrada hasta el momento en el próximo pico Aparece una onda sinusoidal y repite el ciclo de carga de este capacitor, lo que da como resultado el voltaje constante pico requerido a través de él.

Este proceso de carga del condensador en cada ciclo máximo de la CA exige que la entrada esté equipada con suficiente corriente para cumplir con el consumo de carga del SMPS, entre estos intervalos pico.

El ciclo se implementa descargando rápidamente una gran corriente en el condensador, que se aplica a la carga mediante la descarga hasta que llega el siguiente ciclo máximo.

Para este patrón de carga y descarga desigual, se recomienda que la corriente de pulso del capacitor sea un 15% más alta que el requisito promedio de la carga.

Podemos ver en la figura anterior que a pesar de la cantidad significativa de distorsión, los parámetros de voltaje y corriente aparentemente están en fase entre sí.

Sin embargo, si aplicamos el término 'coseno de ángulo de fase' a lo anterior, daría lugar a una inferencia incorrecta con respecto a que la fuente de alimentación tiene un factor de potencia de 1.0.

Las formas de onda superior e inferior indican la cantidad de contenido armónico de la corriente.

Aquí el 'contenido armónico fundamental' se indica en comparación con una amplitud del 100%, mientras que los armónicos más altos se presentan como los porcentajes suplementarios de la amplitud fundamental.

Sin embargo, dado que la potencia real está determinada solo por el componente fundamental, mientras que los otros armónicos suplementarios solo representan la potencia aparente, el factor de potencia real puede estar bastante por debajo de 1.0.

Llamamos a esta desviación por el término factor de distorsión que es fundamentalmente responsable de dar lugar a un factor de potencia no unitario en las unidades SMPS.

Expresión de poder real y aparente

Una expresión general que aborda la conexión entre el poder real y el aparente se puede dar de la siguiente manera:

Donde cosΦ forma el factor de desplazamiento que emerge del ángulo de fase Φ entre las formas de onda de corriente / voltaje y cosΦ significa el factor de distorsión.

Refiriéndonos al diagrama a continuación, podemos presenciar una situación que muestra una corrección perfecta del factor de potencia.

Podemos ver que aquí la forma de onda de la corriente replica de manera ideal la forma de onda de voltaje, ya que ambas aparentemente están funcionando en fase y sincronizadas entre sí.

Por lo tanto, aquí se podría suponer que los armónicos de la corriente de entrada son casi cero.

Corrección del factor de potencia versus reducción armónica

Al observar las ilustraciones anteriores, es evidente que el factor de potencia y los armónicos bajos funcionan en sincronía entre sí.

En general, se percibe que si se describen los límites para los respectivos armónicos, podría ayudar a restringir la contaminación de la corriente de entrada en las líneas eléctricas al eliminar las perturbaciones de corriente que interfieren con los otros aparatos cercanos.

Por lo tanto, mientras que el procesamiento de la corriente de entrada puede denominarse 'corrección del factor de potencia', la magnitud del refinamiento de salida se considera que este procesamiento se entiende como contenido armónico según las directrices internacionales.

Para las topologías SMPS, normalmente es el elemento de desplazamiento el que está aproximadamente en la unidad, lo que da lugar a las siguientes relaciones entre el factor de potencia y la distorsión armónica.

En la expresión el THD representa la Distorsión Armónica Total como la suma cuadrática de los armónicos dañinos sobre el contenido fundamental, expresando el peso relativo del contenido armónico asociado con referencia a la contraparte fundamental La otra ecuación asocia la figura absoluta del THD y no en la proporción de%, expresando que THD necesita ser esencialmente cero para crear un PF unitario.

Tipos de corrección del factor de potencia

La característica de forma de onda de entrada en la figura anterior demuestra un tipo típico 'activo' de corrección del factor de potencia para un dispositivo SMPS introducido entre una configuración de rectificador de entrada y un condensador de filtro, y a través de un circuito integrado PFC que controla los procedimientos junto con los circuitos asociados para asegurándose de que la corriente de entrada siga cohesivamente la forma de onda del voltaje de entrada.

Este tipo de procesamiento puede considerarse como el tipo más común de PFC empleado en los circuitos SMPS modernos, como puede verse en la figura siguiente.

Habiendo dicho esto, de ninguna manera es obligatorio que sólo se utilicen versiones 'activas' que utilicen circuitos integrados y semiconductores para el PFC propuesto. Normalmente, se agradece cualquier otra forma de diseño que pueda garantizar una cantidad razonable de PFC por debajo de las regulaciones establecidas.

Se ha observado que, de hecho, un solo inductor que reemplaza la posición de la contraparte 'activa' es capaz de rechazar satisfactoriamente los armónicos controlando los picos y distribuyendo la corriente uniformemente en sincronía con la tensión de entrada de manera bastante eficiente.

Diseño PFC pasivo

Sin embargo, esta forma de control pasivo de PFC podría exigir un inductor con núcleo de hierro significativamente voluminoso y, por lo tanto, se puede utilizar para aplicaciones en las que la compacidad no es un requisito crucial. (pagina 12)

Un solo inductor pasivo podría parecer una solución rápida para PFC, pero para aplicaciones de alta potencia, el tamaño podría comenzar a perder interés debido a sus dimensiones impracticablemente grandes.

En el siguiente gráfico podemos observar las características de entrada de tres números de variantes de SMPS de PC de 250 vatios, cada uno de los cuales representa una forma de onda de corriente en un factor de escala equivalente.

Podemos ver fácilmente que el resultado obtenido de un PFC basado en inductor pasivo es un 33% más de picos de corriente que con el filtro PFC activo.

A pesar de que esto puede pasar los estándares IEC61000-3-2, definitivamente no estará a la par con la regla de requisitos 0.9PF más estricta reciente y fallaría el nivel de aceptación de QC, establecido según estos nuevos estándares.

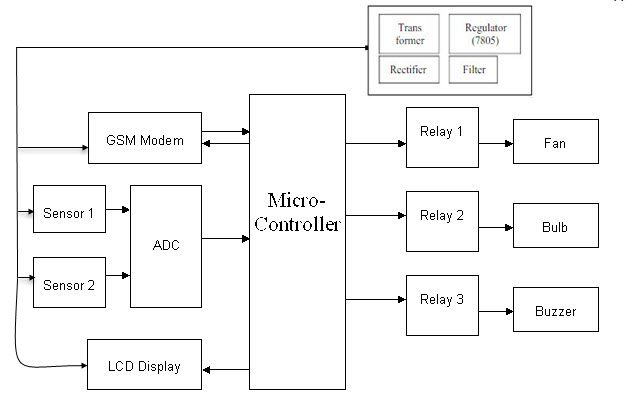

Diagrama de bloques básico

Debido a la tendencia actual del mercado electrónico, donde podemos ver un aumento en los costos del cobre junto con el aumento en el proceso de núcleos magnéticos y la introducción de materiales semiconductores modernos y mucho más baratos, no será una sorpresa si notamos el enfoque PFC activo. volviéndose extremadamente popular que la contraparte pasiva.

Y se podría percibir que esta tendencia crecerá aún más en el futuro próximo, presentando soluciones PFC cada vez más avanzadas y mejoradas para los muchos diseñadores y fabricantes de SMPS.

Comparación de los armónicos de la línea de entrada con los estándares IEC610003-2

En la Figura siguiente, podemos ver rastros de tres resultados SMPS de PC de 250 vatios separados con referencia a las restricciones de IEC6000-3-2. La restricción indicada es válida para todos los dispositivos de clase D, como PC, televisores y sus monitores.

El límite de contenido de armónicos mostrado se fija de acuerdo con la potencia de entrada de los dispositivos. Para productos relacionados con luces como luces LED, luces CFL, normalmente se siguen las restricciones de clase C, que están idénticamente a la par con sus límites de potencia de entrada.

Otros productos electrónicos no convencionales encuentran su límite de PFC establecido en proporción a una potencia de entrada mínima de 600 vatios.

Si miramos la traza pasiva de PFC, encontramos que apenas se ajusta al límite de restricción establecido, solo un tipo de situación de tocar y listo (en el armónico no3)

Análisis de las funciones de PFC pasivo

En la siguiente figura podemos ver un ejemplo clásico de circuito PFC pasivo diseñado para una fuente de alimentación de PC tradicional. Lo notable aquí es la conexión de la toma central del inductor PFC con el voltaje de entrada de la línea de entrada.

Mientras está en el modo de selección de 220 V (interruptor abierto), las dos secciones completas del inductor se aplican con la red del rectificador funcionando como un circuito rectificador de puente completo.

Sin embargo, en el modo de 110 V (interruptor cerrado), solo el 50% o la mitad de la bobina se utiliza a través de la sección del lado izquierdo de la bobina que se está implementando, mientras que la sección del rectificador ahora se transforma en un circuito doblador rectificador de media onda.

Dado que la selección de 220 V está destinada a generar alrededor de 330 V después de la rectificación de onda completa, esto forma la entrada de bus para el SMPS y posee la posibilidad de fluctuar significativamente de acuerdo con el voltaje de la línea de entrada.

Ejemplo de diagrama de circuito

Aunque este diseño de PFC pasivo puede parecer bastante simple e impresionante con su rendimiento, puede presentar algunos inconvenientes notables.

Junto con la naturaleza voluminosa del PFC, otras dos cosas que afectan su rendimiento son, en primer lugar, la inclusión de un interruptor mecánico que hace que el sistema sea vulnerable a un posible error humano mientras se opera la unidad, y también los problemas de desgaste asociados.

En segundo lugar, la no estabilización del voltaje de línea da como resultado ineficiencias relativas en los frentes de rentabilidad y precisión de conversión de potencia de CC a CC vinculada con la salida de PFC.

Controladores de modo de conducción crítica (CrM)

La etapa del controlador llamada modo de conducción crítica, que también se denomina controlador de modo de transición o modo de conducción límite (BCM), son configuraciones de circuitos que se pueden encontrar empleadas de manera efectiva en aplicaciones de electrónica de iluminación. Aunque es fácil de usar, estos controladores son relativamente caros.

El siguiente diagrama 1-8 demuestra un diseño de circuito de controlador CrM regular.

Normalmente, un controlador de CrM PFC poseerá el tipo de circuito que se muestra arriba, que se puede entender con la ayuda de los siguientes puntos:

Una entrada de una etapa multiplicadora de referencia recibe una señal dimensionada apropiadamente de una salida del amplificador de error asociado que tiene un polo de baja frecuencia.

La otra entrada del multiplicador se puede ver referenciada con una tensión fijada de CC estabilizada extraída de una entrada de línea de CA rectificada.

Por lo tanto, la salida resultante del multiplicador es el producto de la CC relativa de la salida del amplificador de error y la señal de referencia en forma de pulsos sinusoidales de CA de onda completa de la entrada de CA.

Esta salida de la etapa del multiplicador se puede ver también en forma de pulsos de onda sinusoidal de onda completa, pero adecuadamente reducida en proporción con el uso de la señal de error aplicada (factor de ganancia) como referencia para el voltaje de entrada.

La amplitud de la señal de esta fuente se ajusta adecuadamente para implementar la potencia promedio especificada correcta y garantizar un voltaje de salida regulado adecuado.

La etapa que es responsable de procesar la amplitud de la corriente hace que la corriente fluya de acuerdo con la forma de onda de salida del multiplicador, sin embargo, se puede esperar que la amplitud de la señal de la corriente de frecuencia de línea (después del suavizado) sea la mitad de la de esta referencia de la etapa del multiplicador. .

Aquí, las operaciones por circuitos de conformación de corriente pueden entenderse como sigue:

Refiriéndose al diagrama anterior, Vref representa la señal de salida de la etapa del multiplicador, que se alimenta a uno de los amplificadores operacionales de un comparador cuya segunda entrada está referenciada con la señal de forma de onda actual.

En el interruptor de encendido, la corriente a través del inductor aumenta lentamente hasta que la señal a través de la derivación alcanza el nivel Vref.

Esto obliga al comparador a cambiar su salida de encendido a apagado apagando la alimentación del circuito.

Tan pronto como esto sucede, el voltaje que estaba aumentando gradualmente a través del inductor comienza a caer lentamente hacia cero y una vez que toca cero, la salida del opamp se revierte y se enciende nuevamente, y el ciclo continúa repitiéndose.

Como significa el nombre de la característica anterior, el patrón de control del sistema nunca permite que la corriente del inductor se dispare por encima del límite predeterminado a través de los modos de conmutación continuo y discontinuo.

Esta disposición ayuda a predecir y calcular la relación entre el nivel de corriente pico promedio de la salida resultante del amplificador operacional. Dado que la respuesta es en forma de ondas triangulares, el promedio de la forma de onda significa exactamente el 50% de los picos reales de las formas de onda triangulares.

Esto implica que el valor promedio resultante de la señal actual de las ondas triangulares sería = Corriente del inductor x sentido R o simplemente poner la mitad del nivel de referencia preestablecido (Vref) del opamp.

La frecuencia de los reguladores que utilizan el principio anterior dependerá del voltaje de línea y la corriente de carga. La frecuencia podría ser mucho más alta con voltajes de línea más altos y podría variar a medida que varía la entrada de línea.

Modo de conducción crítica con sujeción de frecuencia (FCCrM)

A pesar de su popularidad en diversas aplicaciones de control de PFC de suministro de energía industrial, el controlador CrM explicado anteriormente implica algunos inconvenientes inherentes.

La principal falla de este tipo de control PFC activo es su inestabilidad de frecuencia con respecto a las condiciones de línea y carga, que muestra un aumento de frecuencia con cargas más ligeras y voltajes de línea más altos, y también mientras cada vez que la onda sinusoidal de entrada se acerca a los pasos por cero.

Si se intenta corregir este problema agregando una abrazadera de frecuencia, se obtiene una salida con una forma de onda de corriente distorsionada, lo que parece inevitable debido al hecho de que “Ton” permanece sin ajustar para este procedimiento.

Sin embargo, el desarrollo de una técnica alternativa ayuda a lograr una verdadera corrección del factor de potencia incluso en el modo discontinuo (DCM). El principio de funcionamiento se puede estudiar en la Figura siguiente y con las ecuaciones adjuntas.

Con referencia al diagrama anterior, la corriente máxima de la bobina se puede evaluar resolviendo:

La corriente media de la bobina con referencia al ciclo de conmutación (que además se asume como la corriente de línea instantánea para el ciclo de conmutación dado, debido al hecho de que la frecuencia de conmutación suele ser mayor que la frecuencia de línea en la que se producen las variaciones de la tensión de línea ), se expresa con la fórmula:

La combinación de la relación anterior y la simplificación de los términos da lo siguiente:

La expresión anterior indica e implica claramente que en caso de que se implemente un método en el que un algoritmo se encargue de mantener ton.tcycle / Tsw a un nivel constante, nos permitiría lograr una corriente de línea de onda sinusoidal que tenga un factor de potencia unitario incluso en el discontinuo modo de operación.

Aunque las consideraciones anteriores revelan algunos beneficios distintos para la técnica del controlador DCM propuesta, no parece ser la opción ideal debido a los altos niveles de corriente pico asociados, como se demuestra en la siguiente tabla:

Para lograr unas condiciones ideales de PFC, un enfoque sensato sería implementar una condición en la que los modos de operación DCM y Crm se fusionen para obtener lo mejor de estas dos contrapartes.

Por lo tanto, cuando las condiciones de carga no son pesadas y el CrM funciona a alta frecuencia, el circuito pasa a un modo de operación DCM, y en caso de que la corriente de carga sea alta, se permite que la condición Crm persista para que los picos de corriente lo hagan. no tienden a cruzar los límites altos indeseables.

Este tipo de optimización en los dos modos de control sugeridos se puede visualizar mejor en la siguiente figura, donde los beneficios de los dos modos de control se combinan para lograr las soluciones más deseables.

Continúa el modo de conducción

El modo de conducción continua de PFC podría volverse bastante popular en los diseños SMPS debido a su característica y rango de aplicación flexible y las diversas ventajas asociadas.

En este modo, la tensión máxima actual se mantiene a un nivel más bajo, lo que resulta en pérdidas de conmutación minimizadas dentro de los componentes relevantes y, además, la ondulación de entrada se presenta a un nivel mínimo con una frecuencia relativamente constante, lo que a su vez permite que el proceso de suavizado sea mucho más simple para lo mismo.

Los siguientes atributos asociados con el tipo CCM de PFC deben discutirse un poco más detalladamente.

Vrms2 Control

Uno de los atributos vitales con la mayoría de los diseños de PFC aplicados universalmente es la señal de referencia, que debe ser una imitación escalonada del voltaje de entrada rectificado.

Este equivalente rectificado minimizado del voltaje de entrada se aplica finalmente en el circuito para dar forma a la forma de onda correcta para la corriente de salida.

Como se discutió anteriormente, normalmente se emplea una etapa de circuito multiplicador para esta operación, pero como sabemos, una etapa de circuito multiplicador podría ser relativamente menos rentable que un sistema multiplicador de entrada twn tradicional.

Se puede observar un diseño de ejemplo clásico en la Figura siguiente, que demuestra un enfoque de PFC en modo continuo.

Como se puede ver, aquí el convertidor elevador se activa con la ayuda de un PWM en modo corriente promedio, que se encarga de dimensionar la corriente del inductor (corriente de entrada para el convertidor), con referencia a la señal de corriente de comando, V (i) , que puede verse como el equivalente reducido del voltaje de entrada V (pulg) a una proporción de VDIV.

Esto se implementa dividiendo la señal de voltaje de error por el cuadrado de la señal de voltaje de entrada (suavizado por el condensador Cf, para crear un factor de escala simplificado con referencia al nivel de voltaje de entrada).

Aunque puede resultarle un poco incómodo ver que la señal de error se divide por el cuadrado del voltaje de entrada, la razón detrás de esta medida es crear una ganancia de bucle (o una respuesta transitoria dependiente) que puede no estar basada en el voltaje de entrada desencadenante.

La cuadratura del voltaje en el denominador se neutraliza con el valor de Vsin junto con la función de transferencia del control PWM (la proporcionalidad de la pendiente del gráfico de corriente del inductor con el voltaje de entrada).

Sin embargo, una desventaja de esta forma de PFC es la flexibilidad del multiplicador, que obliga a esta etapa a estar un poco sobrediseñada, especialmente en las secciones de manejo de energía del circuito, de modo que pueda soportar incluso los peores escenarios de disipación de energía.

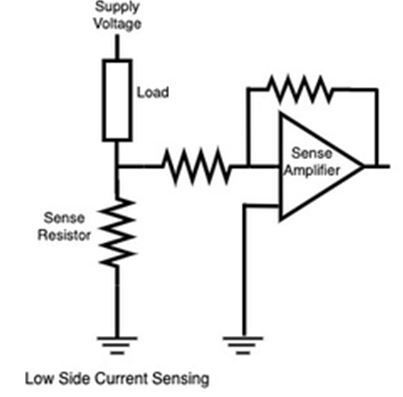

Control de modo de corriente promedio

En la figura anterior podemos ver cómo la señal de referencia producida a partir del multiplicador V (i) significa la forma de la forma de onda y el rango de escala de la corriente de entrada PFC.

La etapa PWM indicada se hace responsable de asegurar que una corriente de entrada promedio esté a la par con el valor de referencia. El procedimiento se ejecuta a través de una etapa de controlador de modo de corriente promedio, como se puede ver en la figura que se muestra a continuación.

El control del modo de corriente promedio está básicamente configurado para regular la corriente promedio (entrada / salida) con referencia a la señal de control Icp, que a su vez se crea empleando un bucle de CC de baja frecuencia a través de una etapa de circuito amplificador de error, y esto no es más que la corriente equivalente correspondiente a la señal Vi que se muestra en la figura anterior a este.

El amplificador de corriente de etapa funciona como un integrador de corriente y también como un amplificador de error, para regular la forma de la forma de onda, mientras que la señal Icp que se genera a través de Rcp se hace responsable de ejecutar el control de voltaje de entrada de CC.

Para garantizar una respuesta lineal del amplificador de corriente, se requiere que su entrada sea similar, lo que significa que la diferencia de potencial generada a través de R (derivación) debe ser similar al voltaje generado alrededor de Rcp, porque no podemos tener una CC a través del Entrada de resistencia no inversora del amplificador de corriente.

Se supone que la salida generada por el amplificador de corriente es una señal de error de 'baja frecuencia' que depende de la corriente promedio de la derivación, así como de la señal del Isp.

Ahora, un oscilador genera una señal de diente de sierra que se usa para comparar la señal anterior con él, tal como se hizo con el diseño de control del modo de voltaje.

Esto da como resultado la creación de PWM determinados comparando las dos señales mencionadas anteriormente.

Soluciones PFC avanzadas

Los diversos métodos de controles PFC descritos anteriormente (CrM, CCM, DCM) y sus variantes proporcionan a los diseñadores opciones variadas para configurar circuitos PFC.

Sin embargo, a pesar de estas opciones, la búsqueda constante de lograr módulos mejores y más avanzados en términos de eficiencia ha permitido diagnosticar diseños más sofisticados para estas aplicaciones.

Hablaremos más sobre esto ya que este artículo se actualiza con lo último sobre el tema.

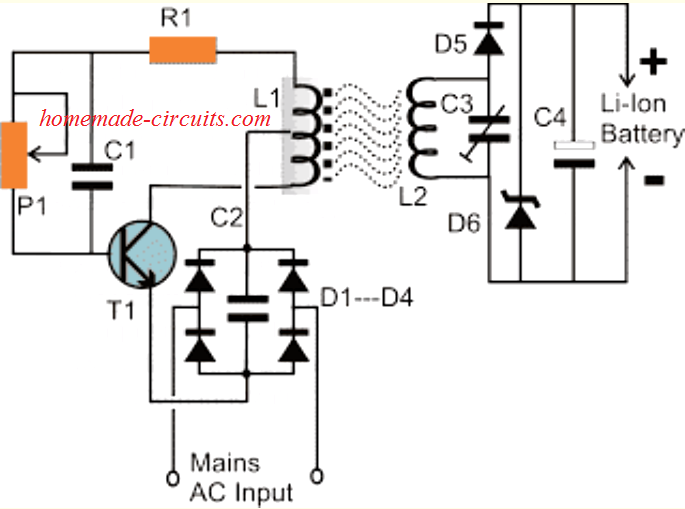

Anterior: Cómo seleccionar el cargador adecuado para la batería de iones de litio Siguiente artículo: Circuito Solar E Rickshaw